LEO Satellite Ground Communication Chips and Modules

技術簡介

全球低軌衛星地面通訊設備市場蓬勃發展,臺灣具有資通訊、IC 設計及半導體製造技術等優勢。但地面設備之天線陣列,需數百顆以上射頻晶片與基頻控制晶片整合之陣列天線模組,目前仍仰賴國外進口,國內產業亟須補足射頻與控制晶片及陣列天線模組化之次系統自主技術能量,以提升晶片及系統模組廠之產品價格競爭力。為此,ITRI專注開發地面設備關鍵核心晶片技術(如射頻晶片、波束追蹤控制晶片等),並進行新式天線模組整合技術,以最佳化產業布局,協助達成布局我國低軌衛星地面通訊設備射頻前端核心技術自主技術能量。核心技術產出包含

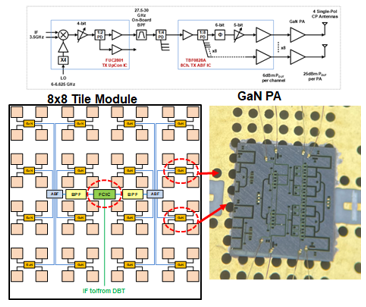

- 降低成本關鍵之波束成型射頻晶片:可應用於Ka band發射端與接收端之波束成型晶片含功率放大器、低雜訊放大器、相位與增益控制CMOS電路

- 提升製程良率之多磚塊可擴充陣列天線模組設計:以磚瓦式設計之射頻前端模組可拼接高傳輸大型陣列系統或物聯網微型化模組

- 微型化模組關鍵之GaN功率放大器:以氮化鎵製程製作Ka band功率放大器,提高輸出功率以降低陣列天線數量與射頻模組體積

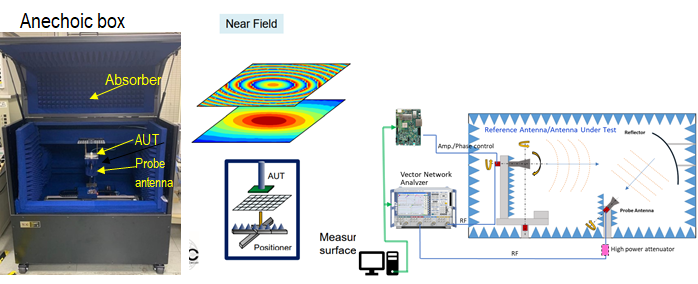

- 快速天線校正之演算法開發:整合波束成型晶片與陣列天線模組之波束天線出廠前校正,加快測試開發時程。提供可校正波束成型天線場型降低天線陣列指向誤差與維持最大輸出功率

- 波束追蹤控制晶片關鍵電路:通用型衛星天線陣列波束追蹤控制晶片架構,高整合前端射頻及基頻介面架構設計,匹配國際衛星專用晶片組,以數位補償技術、數位波束合成技術開發,降低寬頻天線設計複雜度

圖1 磚瓦式8x8天線陣列模組與射頻前端模組架構圖含GaN功率放大器和CMOS波束成型晶片

圖2 陣列天線模組出廠前校正流程:近場量測校正單一天線與遠場量測校正陣列天線之波束天線場型

技術特色

- 國內自主開發射頻前端晶片整合可擴充磚瓦式8x8相位陣列天線模組

- 可拼接成巨量資料傳輸之大型陣列系統或物聯網連接之微型化模組

- 射頻晶片包含: GaN功率放大器與CMOS收發機射頻晶片ABF/UDC/DBF

- 陣列天線自我校正技術Self-Cal開發與實現快速波束切換Beam Steering以達成追蹤低軌衛星

- DBF晶片I/O介面為Digital IF Interface以實現低軌道衛星與NTN手機互聯

技術規格

- Ka band波束成型射頻晶片射頻前端IC元件設計

- PA OP1dB >= 14 dBm

- PA Gain >= 22 dB

- LNA Gain >= 22 dB

- LNA NF <= 3.5 dB

- 射頻多磚塊可擴充陣列天線模組

- Tx Antenna Array EIRP >= 44 dBm

- Tx Antenna gain >= 32 dBi

- Tx Scan loss < 3dB @ 60⁰ off boresight angle

- Rx NF < 6dB

- Rx Scan loss < 3dB @ 60⁰ off boresight angle

- 快速天線校正演算法:

- Antenna Array Calibration in CATR Technique

- Unnecessary for Phase detection (Power detector for measuring equipment)

- Calibrated Amplitude error: < 1 dB

- Calibrated Phase error: < 2 deg

- Calibrated Point error: < 2 deg

- 波束追蹤控制晶片關鍵電路:

- 頻寬250MHz

- 射頻及基頻介面架構

- 數位補償技術

- 數位波束合成技術

應用範圍

應用於Ka band波束合成射頻晶片之CMOS功率放大器與低雜訊放大器IC設計、評估UT 射頻次系統 Link budget 與架構設計、製作LEO射頻前端模組、波束成型天線場型進行低成本和遠場快速校正、低軌衛星天線陣列系統、電子封裝/模組端熱性能設計與優化

聯絡窗口

聯絡人:洪俊中/新世代通訊技術與應用推廣部(C200)�

電話: 03-5915873�

Email:charlie_hong@itri.org.tw

https://www.itri.org.tw/

工研院資訊與通訊研究所