前言

毫米波傳輸技術已大量使用於點對點通訊、行動網路回傳(Wireless Backhaul)以及新興的非地面網路(Non-Terrestrial Networks,NTN)系統,如低軌道衛星通訊網路(Low-Earth-Orbit Satellite Network)與高空通訊平台(High-Altitude Platform Station,HAPS)。除了常用的6至42 GHz頻段外、包括E-band(71~86 GHz)、W-band(92~114 GHz)、D-band(130-174 GHz)等高頻段可提供大片連續頻譜供巨量通訊使用。實務上由於高頻空間傳輸損耗較大,需使用窄波束大型高增益天線,如碟型天線來克服訊號傳輸距離短與涵蓋範圍較小的問題,同時減少對非通訊目標的電磁干擾(Electromagnetic Interference)。因此難以快速移動波束指向,不易直接用於行動通訊系統。

陣列天線技術可有效解決上述毫米波傳輸的問題,係將大功率發射源與高增益天線分拆為多個小型發射源與小型天線單元,並控制各小型發射源的相位與振幅,使發射信號在遠端之特定空間角度互相疊加增強,形成波束合成(Beamforming)效果,如此即可達到高天線增益並兼具波束電子掃描功能,免除大型笨重機械元件。其中陣列天線系統最關鍵元件:射頻晶片組約占總成本三分之一左右,為各家系統與設備廠商兵家必爭之地。因此以低成本半導體製程完成高效能射頻晶片設計,必將為未來毫米波無線市場商機所在。

精彩內容

1. 毫米波陣列天線晶片組架構

2. 波束合成晶片設計

3. 升降頻轉換晶片設計 |

毫米波陣列天線晶片組架構

由於毫米波段波長較短,為避免陣列天線進行波束掃描時,在非主波束方向產生第二主波束(Second Main Beam),造成波束能量不集中與干擾,造成天線單元實體必須排列緊密,彼此間隔僅約數毫米之距,因此無法利用離散射頻元件製作,機構與散熱也成為嚴苛挑戰。有鑒於此,毫米波陣列天線晶片組需兼具低功耗與高整合度,並依通訊信號品質規範要求線性度與雜訊性能。陣列天線依相位與振幅控制機制可區分為類比與數位兩種波束合成架構。數位波束合成係在數位電路完成相位調整,再升頻至毫米波段發射。而類比波束合成又可分射頻(Radio Frequency)、本地(Local)或中頻(Intermediate Frequency)相位控制法,其中以射頻波束合成最為普遍。

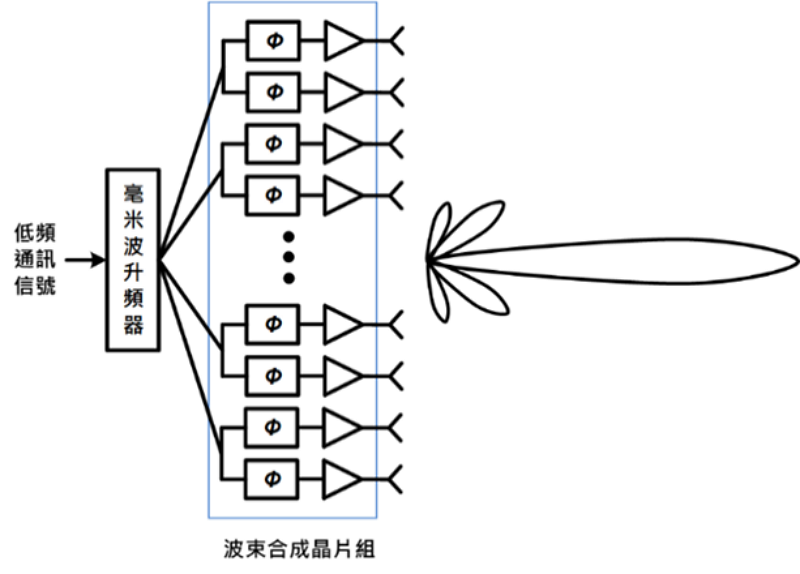

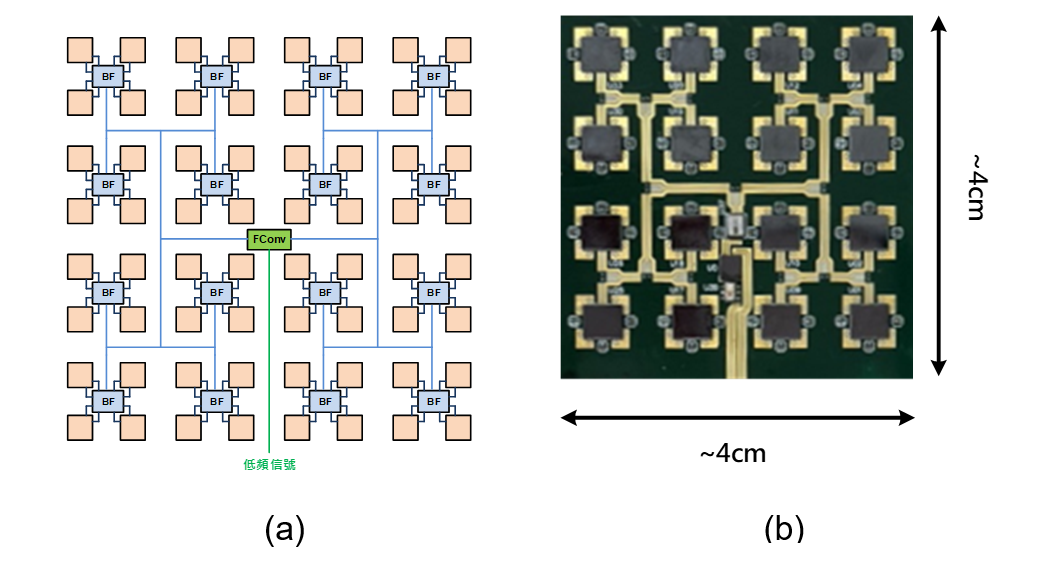

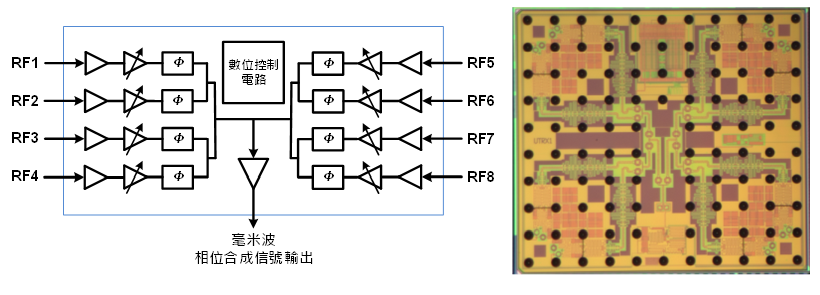

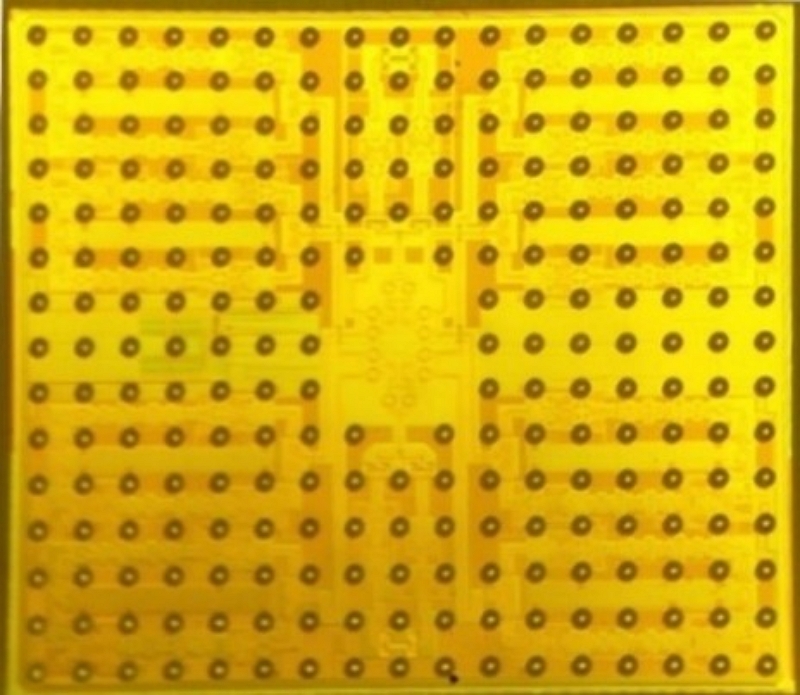

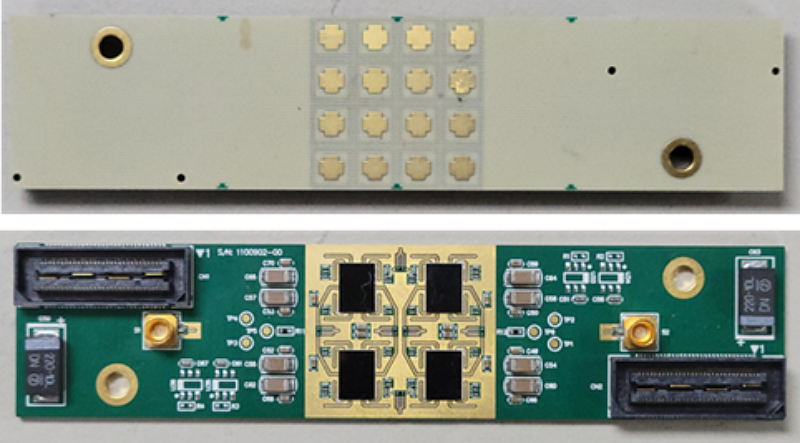

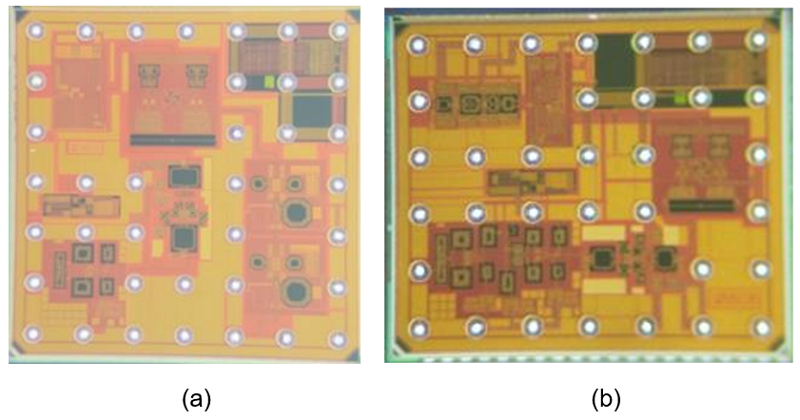

陣列天線進行波束合成的關鍵射頻晶片元件包括波束合成晶片和升降頻轉換晶片,如圖1所示。波束合成晶片負責控制陣列天線中各單元間的振幅與相位差,以進行波束合成與掃描。升降頻轉換晶片則是將毫米波高頻段信號升降轉換為低頻或中頻信號,送往後續信號處理電路與基頻信號處理器進行調變與解調。以圖2(a)之64(8x8)單元雙極化陣列天線為例,控制一組雙極化單元天線需要兩個控制埠,若採高整合8通道波束合成晶片實現需要16顆波束合成晶片(BF)進行控制,另需1顆升降頻轉換晶片(FConv)進行高低頻信號轉換。圖2(b)為該架構之晶片模組實照,於28~30GHz頻段此64天線模組大小僅約4公分X4公分,卻需塞入16顆波束合成晶片與1顆升降頻轉換晶片,對於高頻電路載板信號走線配置與散熱設計均有相當難度。

圖1 陣列天線系統晶片組與波束合成架構

圖2 64(8x8)單元雙極化陣列天線 (a)系統架構 (b)晶片模組實照

波束合成晶片技術

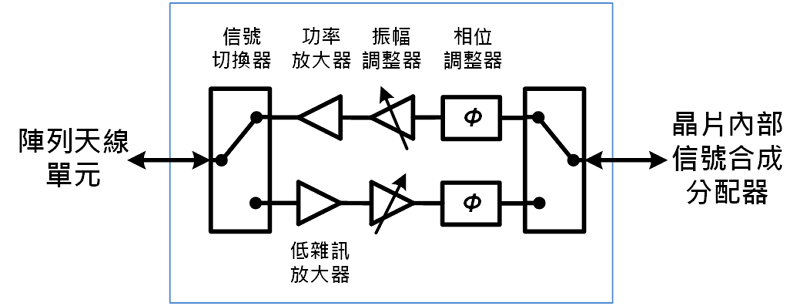

波束合成晶片負責控制各個天線單元之間的振幅與相位差,進行波束的合成和掃描,為最核心之陣列天線晶片組件。其單通道電路架構如圖3所示,其中發射通道與接收通道均須具備振幅與相位控制功能。一般整合4至32組單通道電路於波束合成晶片中,包含前端信號放大器、信號切換器、相位與振幅調整器以及數位控制電路。

圖3 毫米波陣列天線用類比波束合成晶片單通道電路架構(分時雙工模式)

波束合成晶片之前端信號放大器幾可決定陣列天線的特性指標:等效全向輻射功率(Equivalent Isotropic Radiated Power,EIRP)與接收靈敏度(Receiving Sensitivity)。功率放大器(Power Amplifier)做為陣列天線系統之最後級主動元件,其功率輸出將決定EIRP,且常是最耗電元件,其線性度與高功率轉換效率為設計關鍵,以節省功耗並改善散熱問題。低雜訊放大器(Low Noise Amplifier,LNA)做為陣列天線系統接收鏈路之第一級主動元件,其雜訊指數(Noise Figure,NF)與失真特性決定整體陣列天線系統之接收靈敏度。在陣列天線系統設計中,需將低雜訊放大器與功率放大器盡量緊靠天線單元,以避免額外電路板傳輸損耗損傷EIRP與接收靈敏度。

若陣列天線採用分時雙工(Time-Division Duplexing,TDD)模式,則必須使用信號切換器以在不同時槽間於發射與接收模式即時切換,由於信號切換器置於功率放大器、低雜訊放大器與陣列天線單元間,其損耗與線性度、隔離度等特性直接影響EIRP與接收靈敏度。若陣列天線系統採用分頻雙工(Frequency-Division Duplexing,FDD)模式,則發射端與接收端波束合成晶片將分開設計,不需使用信號切換器。

相位與振幅調整器用來陣列天線控制各天線單元相位與振幅權重數值,影響波束合成之主波束寬度、指向精確性與旁波束大小。晶片內部半導體元件寄生效應導致主波束指向角度失真、偏移,以及非預期之旁波束過高等問題需透過類比電路抑制或數位校正方式解決。

另外,由於陣列天線常需要快速切換各主波束角度以進行空間波束追蹤與掃描,故需於晶片中設計記憶存儲元件,以將預先設定之相位與振幅權重數值儲存於晶片中,可一次對所有單元天線進行權重數值調整,加速波束合成反應時間。

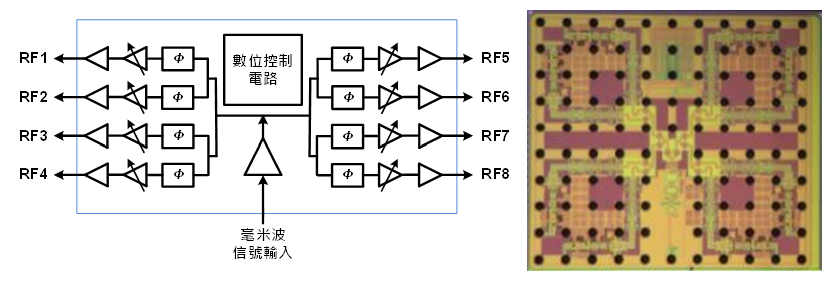

工業技術研究院(以下簡稱工研院)因應上述不同系統架構,分別設計波束合成晶片解決方案如下。圖4及圖5為分頻雙工模式下,毫米波陣列天線用8通道波束合成發射與接收晶片架構與照片圖,其中發射頻段為Ka-band(28GHz)、接收頻段為K-band(19GHz),具5-bit振幅調整與6-bit相位調整功能,輸出功率達與商用晶片匹敵之11dBm水準,其中功率放大器與低雜訊放大器設計兼具高能源效率,使全晶片之消耗功率低至800mW附近,較商用晶片節省約5~10%。接收端亦僅需320mW功率,有效解決散熱需求。

圖4 毫米波陣列天線用8通道Ka-band波束合成發射晶片

圖5 毫米波陣列天線用8通道K-band波束合成接收晶片

圖6為TDD模式下,毫米波陣列天線用8通道波束合成發射與接收晶片照片圖,發射與接收頻段同為Ka-band(28GHz),具4-bit振幅調整與5-bit相位調整功能。其輸出功率達16 dBm較一般商用晶片高,可有效提升系統EIRP值。圖7為以高整合度8通道波束合成晶片實現之16(4x4)單元雙極化TDD陣列天線模組,EIRP可達36 dBm,空間掃描角度達90度。

圖6 毫米波陣列天線用8通道雙極化Ka-band TDD波束合成晶片

圖7 16(4x4)單元雙極化Ka-band TDD陣列天線模組

升降頻轉換晶片技術

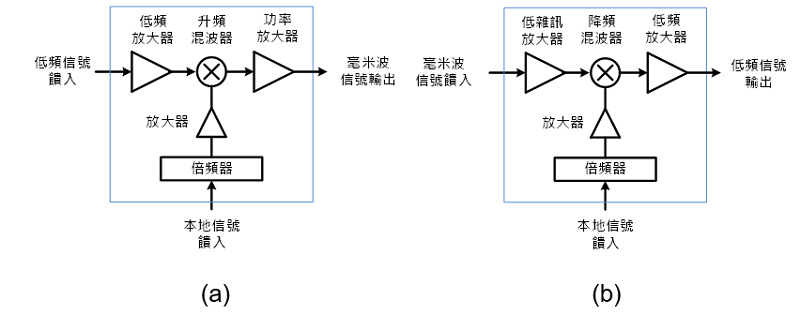

升降頻轉換晶片負責將毫米波高頻段信號升降轉換為低頻信號,並送往基頻處理器進行信號處理,晶片內部包含前端信號放大器、信號切換器、升降頻混波器、本地與低頻信號處理器等元件。圖8為毫米波陣列天線用升頻與降頻轉換晶片之系統架構:

圖8 毫米波陣列天線用(a)升頻與(b)降頻轉換晶片組電路架構

在接收降頻端與發射升頻端之前端信號放大器,與在波束合成晶片中應用之低雜訊放大器與功率放大器取向與特點略有差異。在升降頻晶片中,低雜訊放大器之雜訊指數並非首要考量點,而以線性度與高效率為設計關鍵。功率放大器亦以線性度與高效率為主,以減少信號失真與干擾。若陣列天線系統採用TDD模式,則必須使用信號切換器以在不同時槽間對發射與接收模式進行轉換,若採用FDD模式,則發射端升頻晶片與接收端降頻晶片將分開設計。

升降頻混波器為升降頻轉換晶片之核心元件,可採用主動式或被動式射頻混波架構完成,需具備高轉換增益(Conversion Gain)、高線性度、低雜波干擾、低雜訊等優良特性。實際應用上降頻鏡像與升頻旁波頻帶抑制至少應達到30 dB以上水準,以免除發射頻譜干擾之額外濾波器需求。

由於毫米波段頻率較高,通常無法直接於升降頻轉換晶片中生成低相位雜訊之高頻本地震盪信號,因此會由內外部鎖相迴路(Phase-Locked Loop,PLL)生成較低頻但相位雜訊優良之本地震盪信號,經由倍頻器將低雜訊本地震盪信號提升至毫米波段,再饋入混波器中完成信號升頻與降頻。而低頻放大器必須具有良好增益平坦度及可調增益功能,以調節不同發射與接收功率下之信號強度,使訊雜比(Signal to Noise Ratio,SNR)達到最佳品質。

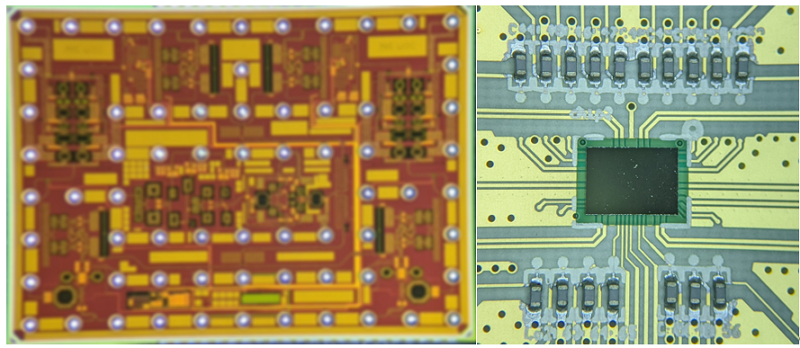

工研院因應上述不同系統架構,已分別開發升降頻轉換晶片解決方案如下:針對非地面網路系統之低軌道衛星FDD應用,有具 11 dBm輸出功率、15 dB轉換增益、30dB升頻旁波頻帶抑制且功率消耗僅350 mW之Ka-band升頻晶片。搭配40 dB轉換增益、32dB增益調整範圍、30dB降頻鏡像抑制與250 mW功率消耗之K-band降頻晶片。兩者皆具低功耗性能,使其特別適用於毫米波段,降低散熱需求,如圖9所示。

圖9 毫米波陣列天線FDD系統用 (a) Ka-band升頻晶片 (b) K-band降頻晶片

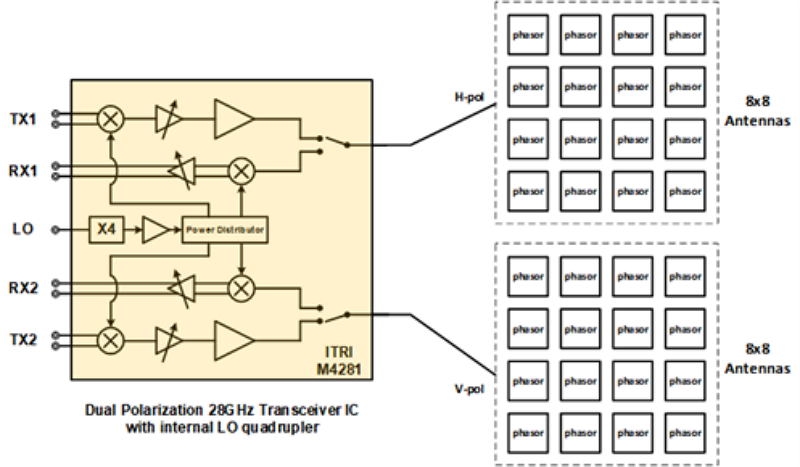

針對一般地面網路系統之TDD應用,對應之Ka-band(n257頻段)雙極化升降頻晶片解決方案具 16 dBm升頻輸出功率、30dB升頻旁波頻帶抑制且功率消耗僅1,500 mW即可推動4倍大小之陣列天線(雙16天線組提升為雙64天線組,如圖10所示)。降頻端具30dB降頻鏡像抑制與僅500 mW功率消耗,除低功耗特性使其特別適用於毫米波段,降低散熱需求外,本晶片亦整合高速Tx/Rx切換器,可於10ns內進行升頻與降頻路徑間轉換,提升TDD系統速度,並具有內部本地信號倍頻電路。其系統架構如圖10所示,實現之晶片與模組照片如圖11所示。

圖10 毫米波陣列天線TDD系統用Ka-band雙極化升降頻晶片架構

圖11 毫米波陣列天線TDD系統用Ka-band雙極化升降頻晶片與模組

結論

整體而言,毫米波陣列系統之射頻晶片組,包含波束合成與升降頻轉換晶片須考量整合度、電源消耗與機構散熱等問題,並針對線性度與雜訊特性等系統要求進行最佳化射頻與數位控制,實現高速高效晶片設計。工研院成功以低成本CMOS半導體製程技術開發完整毫米波陣列射頻晶片組解決方案,包含高能源效率且涵蓋TDD與FDD系統應用之波束合成晶片與升降頻轉換晶片。未來通過模組化設計,可擴展覆蓋範圍、降低能源消耗,滿足未來韌性行動通訊系統的需求。

參考文獻

[1] X. Fu et al., "A Low-Power 256-Element Ka-Band CMOS Phased-Array Receiver With On-Chip Distributed Radiation Sensors for Small Satellite Constellations," in IEEE Journal of Solid-State Circuits, vol. 58, no. 12, pp. 3380-3395, Dec. 2023

[2] A. Ahmed, L. Li, M. Jung, S. Li, D. Baltimas and G. M. Rebeiz, "140-GHz 2-D Scalable On-Grid 8⨉ 8-Element Transmit–Receive Phased Arrays With Up/Down Converters Demonstrating a 5.2-m Link at 16 Gbps," in IEEE Transactions on Microwave Theory and Techniques, vol. 72, no. 5, pp. 2852-2868, May 2024

[3] J. D. Preez, S. Sinha and K. Sengupta, "SiGe and CMOS Technology for State-of-the-Art Millimeter-Wave Transceivers," in IEEE Access, vol. 11, pp. 55596-55617, 2023

[4] F. Tesolin et al., "A Novel LO Phase-Shifting System Based on Digital Bang-Bang PLLs With Background Phase-Offset Correction for Integrated Phased Arrays," in IEEE Journal of Solid-State Circuits, vol. 58, no. 9, pp. 2466-2477, Sept. 2023

[5] J. Park, S. Lee, J. Chun, L. Jeon and S. Hong, "A 28-GHz Four-Channel Beamforming Front-End IC With Dual-Vector Variable Gain Phase Shifters for 64-Element Phased Array Antenna Module," in IEEE Journal of Solid-State Circuits, vol. 58, no. 4, pp. 1142-1159, April 2023