中文摘要

在第四代行動通訊系統中,為達到期待之資料傳輸率與覆蓋性,小型基地台逐漸扮演一個重要的角色。3GPP組織在小型基地台部分,規範了射頻一致性測試,以驗證各廠家所研發之產品品質與互通性。除此之外,一致性測試也是衡量產品的技術成熟度、完整性,並作為進入市場的基本條件之一。本論文介紹一個LTE/LTE-A小型基地台射頻一致性測試平台,可以提供業界在3GPP射頻一致性測試規範之測項服務。

Abstract

Small cell plays an important role of 4G mobile communication system for data rate and coverage. Radio conformance testing (RCT) of small cell, which is used to verify the quality and interoperability of products, is specified in 3GPP standard. RCT is not only used to verify the technology maturity and integrity, but also a basic requirement to market. This paper introduces a radio conformance testbed for LTE/LTE-A small cell, which provides test service of 3GPP RCT for industry.

關鍵詞(Key Words)

長期演進技術(Long Term Evolution;LTE)

小型基地台(Small Cell)

射頻一致性測試(Radio Conformance Testing;RCT)

1. 前言

通訊產品從研發到量產的過程裡需要許多的測試, 過程中會經歷開發平台雛形(Board Prototype)、產品雛形、最後量產階段等不同階段, 每個階段都需要不同的測試進行驗證以確保最終產品品質。

在實體層(Physical Layer, L1)雛形的研發階段,通常會先經歷3GPP組織所規範的射頻一致性測試( Radio Conformance Testing,RCT), 其目的是針對無線電信介面的頻譜以及射頻訊號規定其測試項目、測試流程和測試的通過準則, 此測試適用於規定小型基地台(small cell)的發射機與接收機之基頻訊號處理能力與射頻訊號的功能性, 不僅可以確認廠商開發的設備符合3GPP的規範,更進一步達到支援互通性的要求。

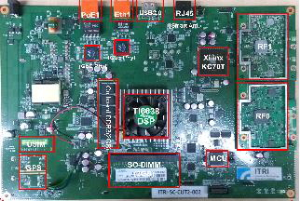

圖 2-1 LTE-A小型基地 台雛形平台

圖 2-1 LTE-A小型基地 台雛形平台2. LTE/LTE-A Small Cell RCT 測試 介紹

2.1 LTE/LTE-A Small Cell 介紹

本系統之LTE-A小型基地台採用軟體無線電架構設計方式,具備高運算能力、高開發彈性,對於未來新增的無線通訊功能可以進行快速的更新,增加產品差異化的特色及競爭力。以本團隊開發之LTE-A小型基地台的硬體雛形平台為例(如圖2-1所示),主要的運算核心是TIC6638 SoC 晶片[1],內含4 顆ARM及8 顆TIC66x DSP, 負責處理LTE-A L1/L2/L3及上層RRM 的功能;RF 模組是採用ADI AD9363transceiver晶片[2],包含AD/DA、PA、LNA以及數位、類比之濾波器,平台具備兩個RF模組介面, 可以實現2個20MHz Carrier Aggregation功能, RF模組與DSP之間則是透過Xilinx FPGA進行資料傳輸介面的轉換以及RF模組的介面控制,另外其他周邊的部分包含兩組Ethernet 介面且其中一組具有PoE++功能,一組USB2.0介面,一組RJ45介面可用來控制Smart antenna,一組USIM介面,以及一組GPS模組介面可以做同步處理。

TI C6638 SoC晶片架構如圖2-2所示,內含8顆TI C66x DSP運算核心,其最高時脈可達1.2GHz,另外還有4顆ARM A15處理器,其最高時脈可達1.4GHz,此外為了提升系統運算的效能, 在晶片內也提供多組符合通訊系統使用的硬體加速器,包含1個Bit Rate Coprocessor(BCP),6 個Fast Fourier TransformCoprocessor (FFTC) ,8 個Viterbi-DecoderCoprocessor(VCP2),4 個Turbo DecoderCoprocessor (TCP3d)。另外目前與FPGA之間的資料傳輸與RF模組的控制介面則是透過其中的SerDes-Based Antenna Interface (AIF2)介面,最多可以使用6個通道,目前操作的速率則是4.9152Gpbs。

LTE-A小型基地台的整體系統架構及功能如圖2-3所示,網路第三層協定以上包含RRC、RRM以及SON等功能是在ARM處理器上實現,網路第二層Upper MAC 以及Upper Scheduler等功能是實作在DSP Core 0,網路第二層Lower MAC以及Lower Scheduler等功能是實現在DSP Core 1,此外MAC層與實體層之間的介面是依據Small Cell Forum所定義的介面PAPI來設計,此部分也是配置在DSP Core 1。網路實體層的發射機(Tx)使用一顆DSP處理器,配置在DSP Core 2,網路實體層的接收機(Rx)則是拆成資料通道以及控制通道,分別配置在DSP Core 3以及DSP Core 4。DSP資料的傳送以及接收是通過AIF2介面直接與FPGA端介接,因此FPGA部分必須實現CPRI介面來承接,同時將資料做格式轉換以符合RF模組所需之LVDS的傳收格式,此外RF模組的參數設定以及控制也是透過CPRI介面接收後再進行解碼及轉發。

2.2 RCT 測試規範介紹

LTE小型基地台在開發雛形階段必須針對射頻訊號分析, 通過射頻一致性測試,以確認開發設備是否符合3GPP TS 36.141規範[3]。在36.141的第六章、第七章及第八章中分別針對不同基地台類型之發射機特性、接收機特性以及接收機效能需求定義測試規範及需求規格。

36.141規範第七章關於基地台接收機的測試包含:

- 參考靈敏度

- 動態範圍

- 通道內選擇性(In-channel selectivity)

- 相鄰通道選擇性(ACS) 及窄頻阻塞(Narrow-band blocking)

- 阻塞(Blocking)

- 混附波輻射波罩(spurious emission)

- 接收互調變(Receiver intermodulation)

36.141規範第八章關於基地台接收機效能的測試包含:

- PUSCH通道性能需求

- PUCCH通道性能需求

- PRACH通道性能需求

3. RCT系統架構

在此章節中,主要是介紹虛擬數據鏈路層virtual-MAC (VMAC)層 與 PHY層 和 Host端 之 間 的 跨 層 控制信號處理設計流程及軟硬體架構,以便能在符合接收機一致性測試RCT的標準規範之下,將測試下鏈(Downlink)資料正確傳輸至向量訊號分析儀(VectorSignal Analyzer,VSA),並正確解碼出向量訊號產生器(Vector Signal Generator,VSG)所產生的控制與上鏈(Uplink)資料來作驗證。 Virtual-MAC主要是定義為規畫測項相關參數的制定, 並控制系統上鏈及下鏈傳輸時序資料的傳遞, 及鏈接Host端和PHY層測試介面,藉此達到良好的軟體控制運作。

3.1 RCT測試硬體架構

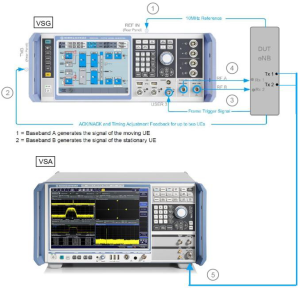

圖3-1為實際VSG及VSA硬體設備對待測物 (Device Under Test,DUT)測試對接圖[5],以下為各個接線訊號說明: 訊號1:VSG會從DUT端reference 10MHz訊號,藉此來作上鏈訊號同步。 訊號2:從DUT端導入ACK/NACK feedback訊號,藉此來作HARQ資料傳輸。 訊號3:導入DUT訊號的frame boundary,以便在正確位置打出上鏈傳輸資訊。 訊號4:DUT接收VSG上鏈傳輸資料, 並將資料作解碼分析。 訊號5:DUT打出下鏈測項訊號至VSA ,並在VSA中設定對應的測試項目以作分析是否符合規範。

圖 3-1 VSG/VSA對接D UT硬體架構

圖 3-1 VSG/VSA對接D UT硬體架構3.2 軟體控制設計架構

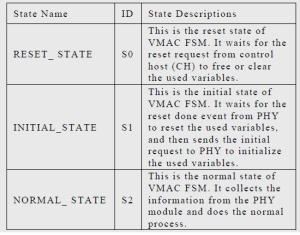

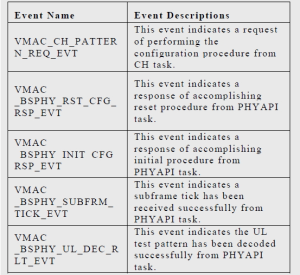

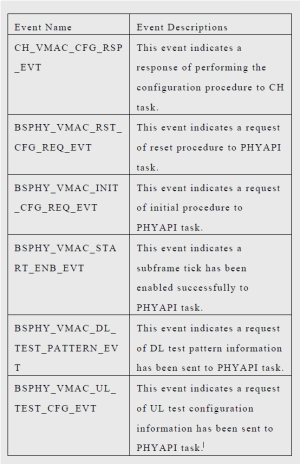

藉由良好的跨層控制參數傳遞,可提高VMAC層與PHY層的系統運作效率,在此軟體架構中,主要提出3 個states及11個VMAC 相關events[4]。如同表3-1所示,主要區分為重置(Reset)、初始化(Initialize)及正規(Normal)三個狀態。 重置狀態為Host端所觸發之介面,其為重置並清除DUT所有FAPI相關的參數, 而初始化狀態為VMAC會將Host端所帶下的參數,分別送至PHY層及初始VMAC層內部訊息, 完成以上兩步驟之後, 則會產生時序訊號並進入正規狀態,此時才可作RCT相關測試與驗證。 表3-2及表3-3分別為描述Host端及PHY層至VMAC層之間的Events傳遞流程。

表 3-1 狀態程序之描述

表 3-1 狀態程序之描述 表 3-2 Host/PHY至VMAC FSM之描述

表 3-2 Host/PHY至VMAC FSM之描述 表 3-3 VMAC至Host/PHY FSM之描述

表 3-3 VMAC至Host/PHY FSM之描述3.3 測試流程設計架構

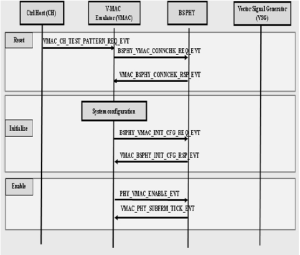

在此針對RCT測試流程之下,主要提出三大跨層控制信號流程架構:初始傳輸控制信號程序、下鏈傳輸程序及上鏈傳輸程序。 3.3.1 初始傳輸控制信號程序 初始傳輸程序是Host端與DUT之間建立資料訊息傳遞的重要程序。只有在完成訊息參數初始化之後,DUT的VMAC層及PHY層才能進行常規的下鏈及上鏈資料傳輸。初始傳輸流程設計架構圖如圖3-2所示,將此程序分為Reset、Initial到Enable三步驟來說明: 步驟Reset: 一開始power on,VMAC會等待Host端傳送觸發訊號至DUT端,在收到Pattern request event之後,代表DUT和Host端已連接成功,此時VMAC會觸發Reset event至PHY層,並作connect確認。 步驟Initial: Reset完之後,VMAC會針對Host端所送出的測試規範制定參數來作系統內部初始化, 並亦初始化PHY層Tx、Rx和RF各個模組相關設定。 步驟Enable: VMAC在確認各個PHY層皆初始化完成之後,即會發送Enable event,此時便完成初始化程序,進入正規狀態, 並開始接收subframe時序上來。

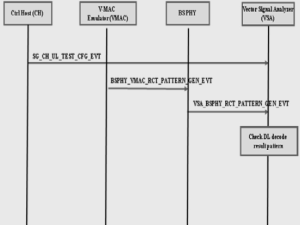

3.3.2 下鏈傳輸控制信號程序

下鏈傳輸程序中,主要是設計為碼框架構 下預排程機制,並藉由跨層控制信號的傳遞,來達到下鏈傳輸資料的配置,其程序如圖3-3所示,在進入正規狀態之後,VMAC則會依序排程每個subframe測試規範相關控制訊號參數及其對應的下鏈傳輸資料,並透過RCT_PATTERN_GEN_EVT送至PHY層,PHY Tx收到資料後,則會在該對應的時間點將測試pattern送出至VSA來作解碼。 VSA在收到DUT資料之前,會先收到Host端所發送的測試項目參數, 及該測項所制定的規範值, 藉此透過這組參數來解譯DUT DL訊號, 並可分析此測項是否符合標準所制定的規範。

圖 3-2 初始傳輸跨層控制信號流程圖

圖 3-2 初始傳輸跨層控制信號流程圖 圖 3-3 下鏈傳輸跨層控制信號流程圖

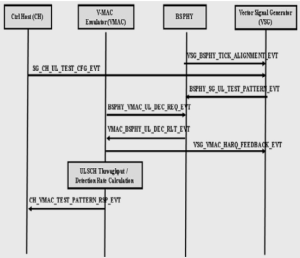

圖 3-3 下鏈傳輸跨層控制信號流程圖3.3.3 上鏈傳輸控制信號程序

在上鏈傳輸程序中,主要亦由VMAC控制上鏈相關的所有參數,藉此在正確的時序上下達指令來對PHY層做各個控制信號解碼動作,其程序如圖3-4所示,以下步驟為流程說明。VSG 會先透過TICK_ALIGNMENT_EVT來和DUT作時序上的同步,藉此在收到Host端所發送的上鏈測試項目參數之後, 便可在與DUT上鏈同步的位置打出訊號。而VMAC在收到Host端所指示的上鏈測項規畫參數之後,則會在上鏈傳輸時間點對PHY層下達控制信號或上鏈資料解碼指令, 藉此算出上鏈傳輸通道資料的吞吐量(Throughput),以及控制訊號的錯誤率(Error rate)和誤判率(False Alarm Rate),而若有資料傳輸時,亦會回報HARQ訊息,藉此來作資訊重傳以便提高吞吐量,最後則會將解碼資訊傳至Host端作上鏈測試報告產出。

圖 3-4 上鏈傳輸跨層控制信號流程圖

圖 3-4 上鏈傳輸跨層控制信號流程圖4. 自動化測試軟體

4.1 軟體架構 (Software Architecture)

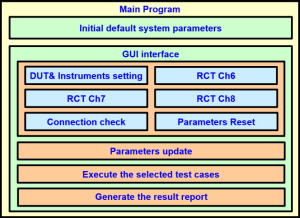

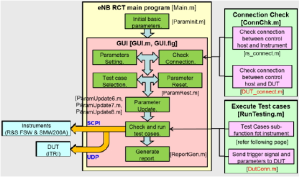

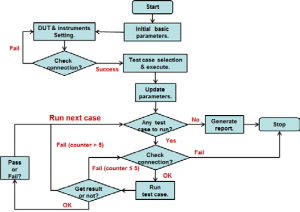

在本文中,依據3GPP RCT測試規範[3]來開發本團隊自動化測試軟體之測試項目。圖4-1所示為自動化測試之軟體架構圖,可分成兩個部分: 第一部分為系統參數初始化,在程式啟動時,會載入程式碼中預設之系統參數,作為測試儀器與DUT的系統設定之參數;第二部分為使用者介面( Graphical User Interface,GUI),該介面能讓使用者選擇3GPP規範中之不同測試案例, 並依需求對案例修改其系統之測試參數。自動化測試軟體會依照使用者所挑選之測試案例逐步測試, 最後藉由VBA語言呼叫word,將其各項測試之量測值與判定結果輸出作成結果報告書。 副程式間關係與運作流程如圖4-2與圖4-3所示。在圖4-3中,能說明自動化測試軟體的開發之設計概念與運作流程順序.

圖 4-1 軟體架構圖

圖 4-1 軟體架構圖 圖 4-2 副程式關係架構圖

圖 4-2 副程式關係架構圖 圖 4-3 軟體流程圖

圖 4-3 軟體流程圖4.2 GUI (Graphical User Interface)

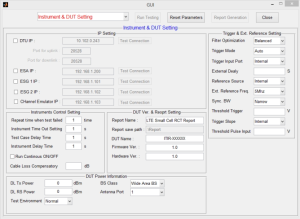

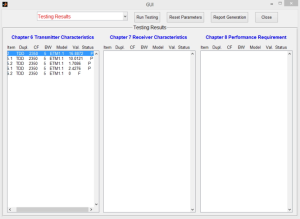

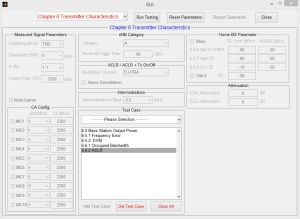

圖4-4~圖4-5為自動化測試軟體之GUI介面。圖4-4為儀器與DUT相關參數之設定畫面,使用者可更改其基本參數,以符合DUT與系統之類型及需求。另有傳送機特性、接收機特性,效能要求之測試項目與參數設定的GUI介面,其分別對應3GPP TS36.141 [3]之6~8章節。在這幾個介面中,可挑選欲測試之項目,並修改其測試參數以符合規範之要求,圖4-5為傳送機特性之GUI介面。 透過儀器回傳之量測數值,再經由程式依法規參考標準判斷其結果,並彙整各項量測結果畫面(如圖4-6所示)。

圖 4-4 GUI介面-Instru ments & DUT Setting

圖 4-4 GUI介面-Instru ments & DUT Setting 圖 4-6 GUI介面-Resul ts

圖 4-6 GUI介面-Resul ts 圖 4-5 GUI介面-Transmitter Characteristics

圖 4-5 GUI介面-Transmitter Characteristics 圖 5-1 6.2 發射功率測試(Total Tx Power)

圖 5-1 6.2 發射功率測試(Total Tx Power)5. 測試結果

在本文中,LTE-A小型基地台之系統設定如下:

● 中心頻率: 2.35GHz

● 頻寬:5MHz

● 類型: TDD-LTE (Local cell)

● 傳輸功率: 18dB

● 測試環境:normal

圖5-1 為6.2 總發射功率測試(Total Tx Power),目的在於測試LTE網路性能, 就像其他空中介面,高度依賴於精確的功率控制。依據3GPP規範之測試標準:a)DUT總發射功須率小於等於24dB;b)DUT標示功率誤差範圍須在正負2.7dB內[3]。本團隊開發之DUT量測結果如下:

● 18.15dB(測試數值) ≤ 24dB;

● (18-18.15)dB ≤ ±2.7dB.

因此總發射功率測試項目, 測試結果是符合指標。

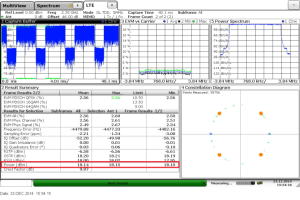

圖 5-2 6.5.1 誤差向量幅度(EVM)

圖 5-2 6.5.1 誤差向量幅度(EVM)圖5-2 為誤差向量幅度(error vectormagnitude, EVM)測試,主要的TX品質測試,波形失真中檢測EVM,EVM使設備準確接收信號的能力下降。根據3GPP規範之測試標準:在QPSK調變下,EVM必須低於9%[3]。本團隊開發之DUT量測結果如下:

● 1.37%(測試數值) < 9%.

因此誤差向量幅度測試項目,測試結果是符合指標。

6. 結論

本篇文章描述了LTE-A小型基地台的系統架構設計,從硬體雛形平台的開發到網路各通訊協定層的軟體開發,系統軟硬體及各層界面的整合,除符合3GGP R8/R9之系統規格,最終為了確保產品品質,也針對雛形平台規畫進行射頻一致性測試。

本計畫建立了射頻一致性測試的系統架構環境,根據測試規範建立測試的標準流程,開發Virtual MAC 層軟體用來介接實體層的FAPI介面,此外為了達到自動化測試,設計了簡易操作的使用者操作界面,透過所開發的控制軟體可以從主機端直接下命令到測試儀器以及受測單元進行各個測項的驗證,最後更可將儀器的測試結果自動化的產生測試報告,讓測試人員可以快速地對測試結果進行判讀。目前在射頻一致性測試規範的第六章到第八章測項已完成建置,相關技術及經驗將可以提供業界LTE/LTE-A小型基地台通過射頻一致性測試。

參考文獻

- TI TCI6638K2K: "Multicore DSP+ARM KeyStone II System-on-Chip (SoC)".

- Analog Device AD9361: "RF Agile Transceiver Data Sheet".

- 3GPP TS 36.141: "Evolved Universal Terrestrial Radio Access (E-UTRA); Base Station (BS) conformance testing".

- 3GPP TS 36.213: "Evolved Universal Terrestrial Radio Access (E-UTRA); Physical layer procedures".

- Rohde & Schwarz, “EUTRA/LTE Digital Standard for R&S®SMW200A User Manual LTE closed-loop BS test, Logfile Generation, ” Rel. 9/Rel. 10, 2014.

作者簡介

謝宗達

資訊與通訊研究所/無線寬頻技術組/基頻設計部工程師, 於2009年取得國立成功大學電機工程研究所博士學位。 2011年服務於資通所。 專長為無線通訊與通道估測演算法。 E-mail:TDHsieh@itri.org.tw

陳宗保

資訊與通訊研究所/無線寬頻技術組/ 基頻設計部副工程師, 於2007年取得國立交通大學電信工程研究所碩士學位。 2008~2009年服務於系統晶片科技中心,2010年起服務於資通所。 專長為無線通訊系統基頻演算法技術。 E-mail:chentsungpao@itri.org.tw

劉俊男

資訊與通訊研究所/ 新興無線應用技術組/ 基頻設計部資深工程師, 於2008年取得中央大學電機工程學系博士學位。 專長為多媒體訊號處理、嵌入式系統設計、基頻硬體電路設計。 E-mail:ChunnanLiu@itri.org.tw