第五代行動通訊(5G)為了提升更好之用戶體驗,提高了傳輸速率、降低傳輸延遲與增加鏈結可靠度。隨著第三代合作夥伴計劃(3GPP)於2018年初步完成Release 15的技術規格,加上臺灣5G商轉預計於2020年底進行,5G於毫米波頻段也是勢在必行,未來毫米波前端晶片與模組的需求會逐年上升。使用頻段升高,意味著傳輸損耗之增加,射頻前端則需提供足夠的等效全向輻射功率(Equivalent Isotropically Radiated Power, EIRP),才可保持相同的訊號涵蓋範圍。為了克服毫米波的傳輸損耗,5G會使用大規模的陣列天線,同時採用波束成形與波束追蹤技術,其中關鍵元件即為相控電路。

精彩內容

1. 毫米波陣列系統設計考量暨相位陣列晶片製程選擇

2. 毫米波相位陣列晶片所包含的電路組成及設計須考量的問題 |

毫米波陣列系統設計考量暨相位陣列晶片製程選擇

毫米波相位陣列

相位陣列技術已發展數十年,過去多運用在軍事、雷達相關用途上[1]。近年由於毫米波的應用蓬勃發展,例如衛星通訊、點對點傳輸、車用雷達與5G等,相位陣列逐漸於民用中興起。相位陣列係使用多天線之系統,由相同訊號分別加上不同權重(weighting),透過不同天線輻射出,在空間中之特定方位同相(in-phase)相加,產生建設性干涉,使能量聚集於該方向,形成波束,進而增加傳輸端的EIRP與接收端的訊雜比(Signal to Noise Ratio, SNR)。

根據權重(也就是相位與振幅)加入的位置,可粗略的區分為類比與數位兩種波束成形架構。其中,類比又可分為在射頻(Radio Frequency, RF)、本地振盪(Local Oscillator, LO)與中頻(Intermediate Frequency, IF)區域作權重調整,各有不同的優缺點[2]。由各個國際大廠Qualcomm、IBM & Ericsson、MediaTek、Samsung、LG等釋出的相關文獻與新聞[3-8]得知,目前5G毫米波係以射頻端做波束成形為主要實現方式,主因不外乎其架構較簡單且成本較低。

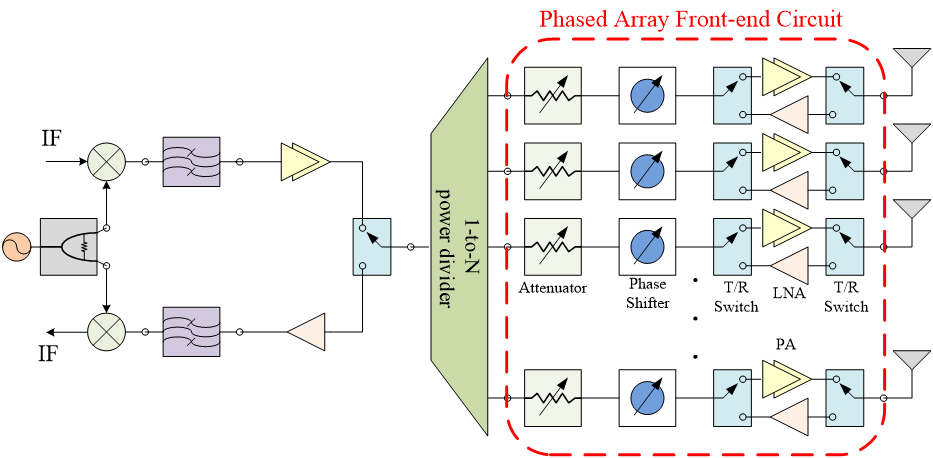

圖1 射頻波束成型之相位陣列前端方塊圖

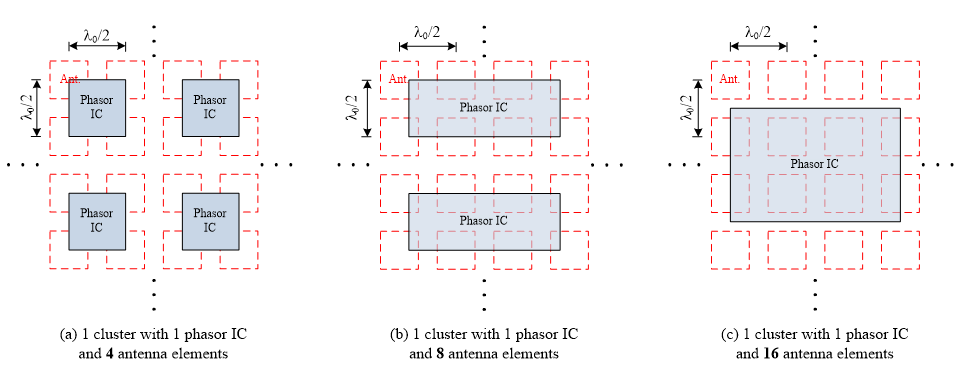

圖1 射頻波束成型之相位陣列前端方塊圖相位陣列為了避免在波束掃描時,產生光柵波瓣(grating lobe),造成波束能量不集中與干擾等問題,一般天線單元之間的間距會限制小於或等於半波長。射頻波束成形之相位陣列前端每一天線單元須包含功率放大器、低雜訊放大器、收發切換開關、相移器與衰減器/可變增益放大器,架構如圖1所示。由於毫米波波長小(28GHz/39GHz波長僅10.7 mm/7.69 mm),要將上述這些分散式元件整合至每一天線單元大小內是十分困難的。另外,在毫米波頻段下,訊號除了無線傳輸有大量損耗外,於基板上之傳輸線損耗也是十分可觀的。因此,在相位陣列設計中,會將功率放大器與低雜訊放大器盡量與天線單元緊密結合,避免多餘傳輸線損耗降低系統整體性能。預期的架構為一整合晶片,囊括多組前端電路,可緊密連接四到十六個天線單元,如圖2。擁有低成本與高整合度等優點的矽製程(如:CMOS、BiCMOS等)是毫米波應用的首選,儘管它的輸出功率與效率不及GaAs和GaN等三五族的製程,但矽製程可將數位電路整合於同一單晶片中,原本數量龐大的相位與振幅控制之數位邏輯訊號輸入/輸出埠,簡化成僅三到五個輸入/輸出埠的序列周邊介面(Serial Peripheral Interface, SPI),大幅降低後端數位硬體的整合複雜度。

圖2 相控陣列整合晶片與天線單元示意圖

圖2 相控陣列整合晶片與天線單元示意圖功耗與散熱

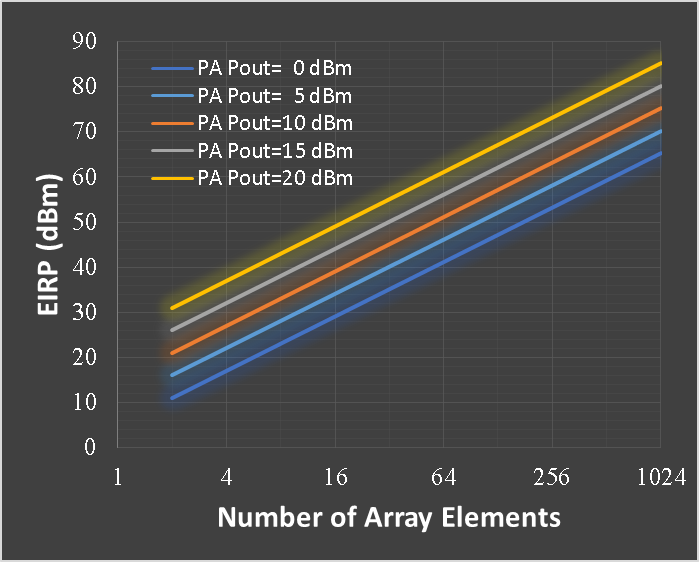

EIRP為電路輸出功率與天線增益的乘積。一個含有M個單元之相位陣列,可額外提供20 Log(M)dB的陣列增益(array gain),這就是空間功率合成(spatial power combining)技術,與一般於基板的傳輸線功率合成相比,少了介質與金屬損耗,相對較為高效。每一個小功率輸出之功率放大器分別饋入獨立天線為一陣列單元,全部輻射功率則為每一陣列單元輻射功率的聚合。以一8×8的陣列天線為例,陣列單元為5 dBi之貼片天線(patch antenna)與10 dBm輸出之功率放大器,其總合EIRP為51 dBm。圖3為陣列單元數目於不同功率放大器輸出功率對EIRP的關係圖,陣列單元數越多,EIRP越大。在EIRP大小固定下,功率放大器輸出功率越大,所需陣列單元數目越少;放大器輸出功率越小,所需陣列單元數目越多。雖然兩者相比,陣列數目少可減少前端電路晶片的用料,或許可降低成本,但輸出功率高則需要消耗較多的直流功率。

圖3 不同PA輸出功率下陣列單元數與EIRP關係圖

圖3 不同PA輸出功率下陣列單元數與EIRP關係圖另外,由於5G採用正交分頻多工(Orthogonal frequency-division multiplexing, OFDM)的調變方式,功率放大器需工作在後退操作點(back-off)才能滿足該調變線性度的要求,後退操作點將會使得直流與射頻功率轉換效率降低,一般功率放大器後退操作點10 dB,其功率轉換效率(Power Added Efficiency, PAE)低於2 %,也就是超過98 %的直流功率全部變成熱。因此,高功率放大器搭配少量陣列單元數,將會面臨較嚴重的散熱問題,散熱系統複雜度與成本會大幅增加。表1以兩顆商用功率放大器為例,一顆線性輸出功率為21 dBm,另一顆則為9 dBm,分別使用4×4與8×8陣列單元,皆可達到50dBm EIRP,但其直流消耗功率卻有將近兩倍的差距,相同條件下的熱模擬分析,前者溫升攝氏295度,後者僅72度。由此可發現使用多陣列單元搭配低功率放大器,可有效避免大直流功耗與散熱問題,也可得知大功率輸出的三五族製程恐無用武之地,相反地,矽製程較為合適。

表1: 相同EIRP下,少陣列單元高功率放大器與多陣列單元低功率放大器比較

|

|

陣列單元

|

陣列增益 (dB)

|

單元Pout/Ga

|

總和Pout/Ga

|

EIRP (dBm)

|

直流功耗(W)

|

溫升 (oC)

|

尺寸 (mm2)

|

|

Case I

|

PA

|

16

|

12

|

21 dBm

|

33

|

50

|

115

|

295

|

16×16

|

|

Antenna

|

16

|

12

|

5 dBi

|

17

|

|

Case II

|

PA

|

64

|

18

|

9 dBm

|

27

|

50

|

64

|

72

|

32×32

|

|

Antenna

|

64

|

18

|

5 dBi

|

23

|

毫米波相位陣列晶片所包含的電路組成及設計須考量的問題

相控整合晶片設計

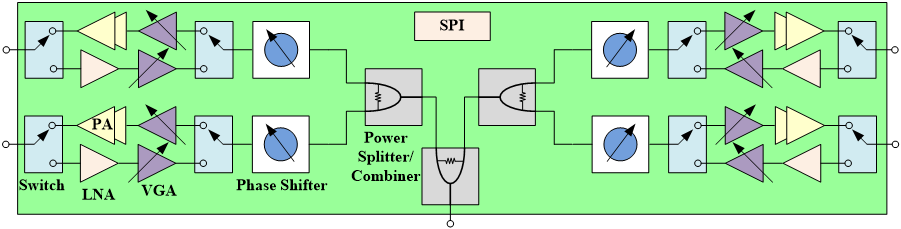

圖4 多路相控晶片方塊圖

圖4 多路相控晶片方塊圖多路相控整合晶片設計,方塊圖如圖4,需整合多個射頻前端電路與數位控制單元,除了佈局本身須注意隔離度問題,每一射頻電路都有其重要指標:

1.功率放大器(Power Amplifier):通常置放於天線單元前最後一級電路,作為訊號放大提升輸出功率,也是陣列天線中決定EIRP的關鍵元件,亦是其中功耗最大的。在毫米波頻段中,電晶體元件本身直流與射頻訊號轉換效率低,加上5G採用線性度要求高的OFDM調變方式,使得功率放大器設計更加不易。如本文前節所述,大功率輸出並不會是設計重點,線性度與高效率才是關鍵。

2.低雜訊放大器(Low Noise Amplifier):通常置放於天線單元後第一級電路,作為射頻訊號接收第一級放大器,其雜訊指數(Noise Figure; NF)影響整體系統之接收靈敏度,故設計重點將在放大信號的同時產生盡可能低的雜訊以及失真。

3.收發切換開關(T/R Switch):有鑑於5G NR毫米波頻段將採用時分雙工(Time-Division Duplexing, TDD),須有切換器轉換發射與接收模態,因此在相位陣列中,收發切換開關為功率放大器、低雜訊放大器與天線單元間的元件,如圖4,故於發射狀態時,切換器之損耗與線性度將會影響最後系統之輸出功率;在接收狀態則會影響雜訊指數與系統接收靈敏度。另外,為避免接收與發射電路產生不穩定甚至振盪的現象,切換器在兩狀態之間的隔離度也是設計重點之一。

4.相移器(Phase Shifter):相位陣列中控制天線單元相位權重的電路,可調整各路之間相位不一致與波束成形,相位變化的解析度與精準度會影響波束成形之方位精準度、增益、半功率波束寬(Half-Power Beamwidth)與旁波瓣水平(Side-lobe level)。另外,由於電路元件本身之寄生效應,相移器做相位切換時會伴隨振幅的變化,也就是相位控制與振幅控制有相依關係,這在相列陣列中會造成波束成形失真的現象。一般做法會以相移器與可變增益放大器(或衰減器)量測數據來校正,取得一組相位與振幅獨立變化之對照表(lookup table),經由該對照表可產生失真較小甚至無失真之波束。若可在相移器電路設計時,將最小化振幅變化加入考量,即可減少後端校正的時間與成本花費。

5.可變增益放大器(Variable Gain Amplifier)或衰減器(Attenuator):相位陣列中控制天線單元振幅權重的電路,可調整各路之間振幅不一致與波束塑型(可降低旁波瓣水平或增加半功率波束寬)。與相移器有著相同寄生效應的問題,在振幅調控時相位會隨之變化,此現象會造成波束失真,可透過校正方式解決,亦或於設計初期透過電路設計抑制相位變化。 總結而言,毫米波前端相控晶片需緊密與天線單元結合,其設計須搭配整體系統,針對整合、功耗與散熱等問題做考量,選擇合適製程,再搭配電路設計優化,減少後段整合校正工作,實現高整合、低成本的前端晶片。

[1] R. J. Mailloux, Phased Array Antenna Handbook. Norwood, MA: Artech House, 2005.

[2] Chun-Hsiang Chi, “Millimeter-wave Phased Array Antenna System for 5G Mobile Communication,” ICT Journal, No.162, pp22-29, Jun. 2015.

[3] J. D. Dunworth et al.,“A 28GHz Bulk-CMOS dual-polarization phasedarray transceiver with 24 channels for 5G user and basestation equipment,” in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers, Feb. 2018, pp. 70–71.

[4] Qualcomm. “Qualcomm Announces the Latest and Smallest Additions in its Family of 5G NR mmWave Antenna Modules. Internet: www.qualcomm.com/, Oct. 22, 2018

[5] B. Sadhu et al., “A 28-GHz 32-element TRX phased-array IC with concurrent dual-polarized operation and orthogonal phase and gain control for 5G communications,” IEEE J. Solid-State Circuits, vol. 52, no. 12, pp. 3373–3391, Dec. 2017.

[6] MediaTek. “MediaTek shows its 5G mmWave antenna design for smartphones. Internet: www.mediatek.com/, Jun. 15, 2018

[7] Roh, W., Seol, J.-Y., Park, J., et al.: ‘Millimeter-wave beamforming as an enabling technology for 5G cellular communications: theoretical feasibility and prototype results’, Commun. Mag., 2014, 52, (2), pp. 106–113

[8] H.-T. Kim et al., “A 28-GHz CMOS direct conversion transceiver with packaged 2×4 antenna array for 5G cellular system,” IEEE J. Solid-State Circuits, vol. 53, no. 5, pp. 1245–1259, May 2018.

相關連結: 回177期_5G及新興應用 專輯