工業技術研究院 資訊與通訊研究所 梁瑋倫 葉凱儀

近年來,人工智能(Artificial Intelligence, AI)的崛起引領積體電路設計(Integrated Circuit design, IC design)領域進入了一個嶄新的時代。隨著硬體運算能力與數據資料的快速增長,以及深度神經網路技術的提升,AI晶片於市場上的競爭也因而愈趨激烈。有鑑於拓展AI晶片市場上無限的商機,工研院資通所晶片設計團隊特別與位居電子設計自動化(Electronic Design Automation, EDA)市場龍頭的新思科技(Synopsys)攜手共同建立人工智慧晶片設計實驗室(AI chip design lab),力求提供晶片設計業者一個嶄新便利的工具平台來開發AI晶片。由新思科技提供EDA工具、矽智財(Silicon Intellectual Property, SIP或Silicon IP)以及快速開發與驗證平台,再由工研院的研發團隊來提供AI系統晶片參考設計與軟硬體客製化技術等服務,針對全速搶攻AI晶片市場進行全球性戰略布局。合作團隊期望藉由所成立的實驗室,來廣結更多業者合力共同開發裝置端AI晶片技術。在協助台灣半導體產業以及AI晶片發展的過程中,無論是對於共同合作的受輔助企業或是新思科技與工研院本身,彼此之間都將因著相互需要,而能在一致的目標下共同成長。

精彩內容

1. 各型態之人工智慧晶片

2. 工研院與新思科技攜手建立實驗室

3. 基於FPGA之晶片驗證工具:ZeBu & HAPS

4. 晶片驗證-硬體仿真加速&原型驗證 |

人工智慧晶片

圖1 各型態AI晶片之間的差異

隨著科技日新月異,因著高科技產品所引領出的AI[1]市場亦愈趨蓬勃發展,與之相輔相成的IC design[2, 3]針對AI層面之應用需求所帶來的改革,也因此愈來愈受到重視。其實,AI晶片並不存在一個十分明確的定義,任何只要能被應用於AI研究領域的晶片,全都可將其稱之為AI晶片。目前,中央處理器(Central Processing Unit, CPU)[4]、圖形處理器(Graphics Processing Unit, GPU)[5]、現場可程式化邏輯閘陣列(Field Programmable Gate Array, FPGA)[6]、特定應用積體電路(Application Specific Integrated Circuit, ASIC)[7]被廣泛地認定為是AI晶片。而由CPU至ASIC的排序中,晶片之通用性不斷降低,然而效能卻逐漸增強(參見圖1)。其中,GPU藉由並行運算所帶來高效率、低成本的優勢,成為目前市場中主要使用的AI晶片;FPGA則是常被許多AI晶片公司拿來驗證ASIC晶片[8];ASIC則是用於實現特定要求所客製化的AI專用晶片。

人工智慧晶片設計實驗室

圖2 人工智慧晶片設計實驗室

縱觀全世界,台灣雖然在晶片設計的領域中具有舉足輕重的影響力[3]。然而,過去台灣在晶片設計的產業裡主要是聚焦在傳統具有標準規範之晶片的應用領域,其中包括無線通訊[9]、影音運算[10]或是有線高速傳輸介面[11]等,而此方面的產業已具備基礎架構、存在固定的設計規則,在軟體開發的層面也相對較為單純。但如今AI機器的時代已來臨,而AI在各種不同的應用情境裡,都必須深入地了解晶片運算能力所能帶出之性能表現。因此,研發AI晶片將面臨針對非標準晶片中之設計與自訂測試標準等方面的挑戰。此外,AI 晶片在應用上所需提供之運算量遠超越傳統晶片,故此需要特別的處理器架構方能滿足。因著我們所遭遇的這一切議題,導致了 AI 晶片於設計流程與功能驗證上相較傳統晶片更為複雜。

因為AI晶片在設計上已不像是過去傳統晶片設計能通過標準通用規範來滿足,這導致目前市場上僅有少數較具規模的晶片設計公司有能力跨足AI晶片設計的領域,而其餘小規模的晶片設計團隊較可能在面對AI晶片設計的過程中遭遇諸多嚴峻的阻礙。為了克服新創開發團隊於AI晶片設計領域裡,所需面對的艱鉅挑戰,人工智慧晶片設計實驗室(AI chip design lab,以下簡稱:AI晶片實驗室)為此因應而生(參見圖2)。由工研院[12]提供晶片設計與驗證服務、新思科技(Synopsys)[13]提供晶片設計工具,而合作對象則是鎖定在較小規模的晶片設計公司,或是不具備晶片設計能力的系統整合(System Integration, SI)[14]業者。透過實驗室的資源與協助,期望能提供晶片業者跨足AI晶片設計一個極佳的解決方案。

AI 晶片實驗室所能提供的服務,包含了軟體與硬體兩個範疇。眾所周知,新思科技是長久以來全球排名第一的電子設計自動化(Electronic Design Automation, EDA)[15] 創新公司,同時也是排名第一的 IC 介面矽智財(Silicon Intellectual Property, SIP 或 Silicon IP)[16] 供應廠商。然而 AI 晶片實驗室所能提供的軟體服務,不僅只侷限於 EDA 軟體這樣的定義,而是更廣義地囊括架構設計、架構模擬、以及參考設計等領域。此外,AI 晶片實驗室目前亦與新思科技合作,共同整合旗下多個矽智財,如:CPU、深度神經網路(Deep Neural Networks, DNN)加速器 [17]、通用序列匯流排(Universal Serial Bus, USB)[18]、行動產業處理器接口(Mobile Industry Processor Interface, MIPI)[19] 等,並藉此設計一個功能強大的 AI SoC(System on a Chip,系統單晶片)[20]。預計以 AI 晶片實驗室的設備先作整合驗證,再以 16 nm 以下製程下線(tape-out)[21] 製造。而這個參考設計,將來會先開放給業界試用,其後再根據不同的應用情境讓業界公司各自客製化。因為主要的架構已經驗證完成,並且 AI 晶片實驗室在軟體方面也有相關經驗,在多種優勢之下更可提高產品上市的速度。

圖3 基於FPGA之 (a)硬體仿真設備ZeBu (b)原型驗證系統HAPS

其次,在硬體設備上,AI 晶片實驗室具有多台性能強大的工作站及 ZeBu [22] / HAPS [13] 驗證平台與軟體。我們可以使用 ZeBu 或 HAPS 這類型的工具,於晶片尚未下線以前,在 AI 晶片系統設計初期實踐早期軟硬體協同發展,用以預測所欲開發之 AI 晶片的性能和瓶頸。其中 ZeBu 平台是快速仿真平台,可提供藉由FPGA進行加速的模擬程序。此外,還可以將一些高速類比電路(例如:USB、PCIE、DDR、MIPI … 等),利用軟體交易器模型(transactor model)來代替,使整個系統可以在ZeBu的平台上來進行驗證。它的原理是將可合成的數位電路合成到 FPGA,而無法合成的類比電路則以 transactor 軟體模型取代。這樣的驗證可以完成作業系統開機,以及應用軟體驗證程序。非常接近實體晶片的工作模式,而非傳統軟體模擬平台,僅能針對各個 IP 做資料讀寫或是進行匯流排協議(bus protocol)[23] 等級的簡單驗證,而要等到純硬體平台的 FPGA 存在之時才能做到作業系統等級的驗證。故此,藉由此種方式來運行,可以提前驗證系統整合後的效能,並且提供多樣化的除錯資訊(例如:waveform dump、UART message … 等),有助於提前找到問題所在。當整個電路需要 n 個節點或 n 個電晶體,若以 FPGA 來進行加速模擬,理論上可使模擬時間與電路複雜度的關係,降到 O(log n)或甚至更低;而傳統的純軟體模擬,則可能高達 O(n2)以上。所以傳統的軟體模擬,不可能做到作業系統開機驗證,而 ZeBu 平台則有辦法駕輕就熟。這使得 ZeBu在 AI/SoC 晶片日益複雜的時代,成為一項不可或缺的驗證利器。

相對ZeBu而言,HAPS則是一個純FPGA硬體的驗證平台。若要在HAPS上驗證,所有的電路都必須要硬體化(包括類比電路),且要驗證的類比IP都需要有對應的晶片(轉接板)。這聽起來似乎比較不友善,但HAPS平台的好處是它的FPGA可以合成到比較快的速度。且相較於ZeBu平台,於編譯完成後,所能執行的速度更快。另外,HAPS平台體積也相對較為輕巧,對有些需要現場驗證的應用項目(例如:通訊、自駕車[24]等)更為適合。故此,兩個平台是各有千秋、相輔相成。

圖3(a)是存放於AI晶片實驗室內之ZeBu,它的內部最多可容納5片FPGA模組,且每一片最大可容納60M gate count電路。這五片模組可以串接使用,也就是最大的容量可達到300M gate count。此外,這5片模組也能分開使用,可以是5個不同的設計在ZeBu上驗證,也可以是相同的設計,由五組人員作不同的IP驗證,很有彈性。圖3(b)是HAPS,AI晶片實驗室內有不同的型號(HAPS-72、HAPS-74及HAPS-80 S104),彼此間主要的差別是關乎速度及容量。就容量而言HAPS-72約25M gate、HAPS-74約50M gate、HAPS-80 S104約100M gate。此外,HAPS還有串接的功能,硬體上它可以經由高速cable互聯,而新思科技的ProtoCompiler軟體也有提供自動切分一個大的設計到不同系統的功能,當然也可以經由使用者手動切分設計。

AI晶片軟硬體設計與系統整合驗證

圖4 硬體仿真加速與原型驗證應用於晶片驗證之流程

AI晶片實驗室所能提供的服務項目,包含了晶片設計、軟體開發到晶片驗證等整套完整的流程。晶片設計屬於硬體範疇,囊括AI晶片架構探索、AI加速器設計、AI晶片系統整合、AI晶片布局與繞線設計實作服務等;軟體開發囊括AI演算法開發、AI系統軟體整合、AI模型優化、AI軟體編輯器、AI應用程式開發等。而晶片驗證則是藉由新思科技所提供的系統驗證設備,統籌了軟硬體驗證的部分。

當積體電路設計完成後,會先利用下線來試生產少量的樣品供應測試,直到測試通過,方可進行大規模量產。待下線完成,若測試失敗,則需再次耗費大量資金重新下線來生產樣品。故此,倘若可以在進行下線之前,藉由模擬與驗證來預知樣品於真實產出後的可靠性與穩定性,並藉此於實際生產前盡可能完善晶片設計,那麼就可以大幅度地提升下線生產後樣品測試的成功率。

FPGA 的屬性是可重複燒錄指定應用的電路到板子上,因為具有可重複燒錄的特性,故此可用來驗證所設計的電路,若有錯誤也可以迅速地將其修正、並再次重新燒錄。反觀,ASIC 於製作完成後,便無法再度更改其中的功能,然而其優勢是執行速度相較 FPGA 為快,且量產下也較 FPGA 能達到更低的成本。FPGA 就是因為具有可重複修改與燒錄之特性,使之成為 ASIC 在下線以前,作為驗證電路設計的有力工具。

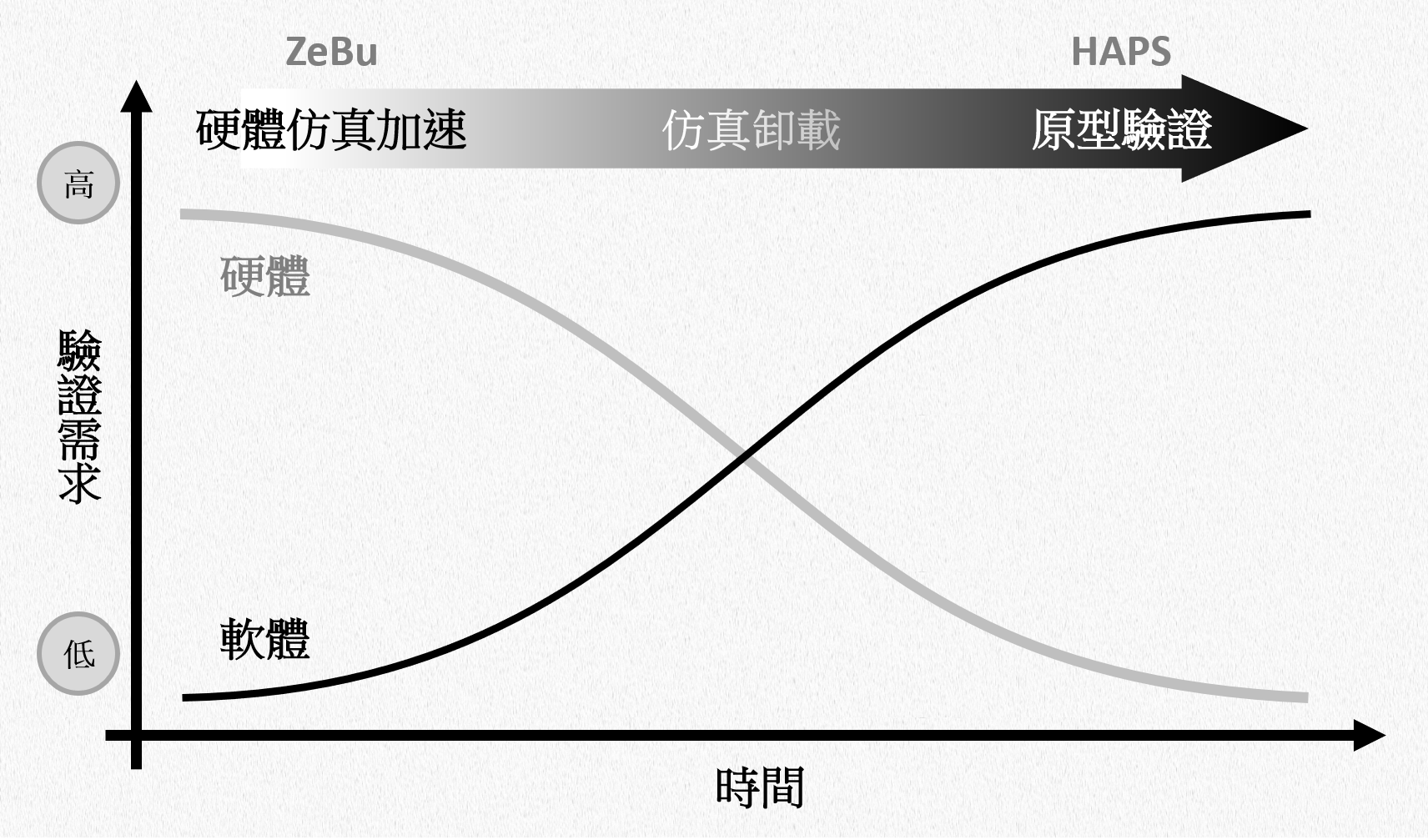

工程師可藉由硬體描述語言(Verilog-HDL 或 VHDL)[25] 將 IC 所需之邏輯以程式描述出來,而所描述的結果,我們稱之為語法轉換層次程式碼(Register Transfer Level code, RTL code)[26]。 藉由 AI 晶片實驗室裡所擁有之基於 FPGA 且功能強大的 ZeBu 與 HAPS 來分別作為硬體仿真加速(emulation)[22] 以及原型驗證(prototyping)[8] 的工具,此兩種工具的關注點不盡相同。我們可以藉由圖4來做說明:於前期 RTL code 驗證階段,傾向於採用硬體仿真加速工具,直到 IC 在硬體設計的成熟度達到比較穩定的階段時,軟體的工作負載便會開始增加,此時即可將設計遷移到原型驗證工具,利用更高的效率來處理軟體測試直至最終進行下線。而由硬體仿真加速轉換到原型驗證的過程,我們將其稱之為仿真卸載(emulation offload)。藉由 ZeBu 與 HAPS 兩者之間適當的搭配與調整,方可使得晶片驗證之各流程達到最為契合的效果。

AI晶片實驗室針對客製化的AI晶片需求,在提供完整的晶片設計、軟體開發到晶片驗證等整套流程之後,還會提供業者詳盡的教育訓練,以及來自於產業科技國際策略發展所(Industry, Science and Technology International Strategy Center, ISTI)、台灣人工智慧晶片聯盟(AI on Chip Taiwan Alliance, AITA)、台灣半導體產業協會(Taiwan Semiconductor Industry Association, TSIA)等AI晶片產業技術領導單位所提供的產業諮詢服務。

此外,實驗室雖名為AI晶片設計實驗室,但卻並非僅能涉足AI晶片的設計,因為AI晶片的設計難度極高,若連高難度的AI晶片設計專案都能接手,傳統的晶片設計自然不在話下。而實驗室中的設備對各種類的晶片設計也都適用,尤其是有複雜架構的SoC。雖然這類的IC在傳統的驗證方法中或許也可以驗證功能,但卻很難驗證效能。例如,在一個真實環境中,CPU/GPU/USB等區塊同時在執行動作,造成各區塊都在搶匯流排資源,因而使得作業系統需要對此進行排程……等,如此複雜的環境存在著各種考量,但晶片在進行下線以前,又需盡其所能地還原晶片於真實環境中的運作狀態,並想辦法改善設計、再預測晶片實際產出後之運作效果是否能有所改良,才能提升下線結束後,樣品測試的成功率。當傳統的工具遠遠不足以滿足驗證上的需求,設計者無法全面周到地考量,等到晶片真的下線才察覺有誤,則為時晚矣!因此,提前使用新的驗證工具才能快速且完善的完成目標。我們希望能藉由實驗室的成立來協助業者縮短開發時程,不僅加速對於晶片設計之相關產品上市的速度,同時也降低其跨足AI晶片設計所需的門檻。

結論

AI科技應用在市場上具有龐大的商機,然而AI晶片在設計上不像傳統晶片有著固定的標準與規範,因此難度較傳統晶片設計為高。有鑑於此,工研院資通所特別與新思科技聯合成立AI晶片設計實驗室,期望能提供業者充足的人力與物力資源,合力協助業者解決此一棘手的問題,帶動台灣AI晶片產業共同成長!

參考文獻

[1] F. Shi et al., “Review of Artificial Intelligence Techniques in Imaging Data Acquisition, Segmentation, and Diagnosis for COVID-19,” IEEE Reviews in Biomedical Engineering, vol. 14, pp. 4-15, 2021.

[2] R. R. Harrison, “The Design of Integrated Circuits to Observe Brain Activity,” Proceedings of the IEEE, vol. 96, no. 7, pp. 1203-1216, 2008.

[3] P. -L. Chang, C. Shih and C. -W. Hsu, “Taiwan's Approach to Technological Change: The Case of Integrated Circuit Design,” Technology Analysis & Strategic Management, vol. 5, no. 2, pp. 173-178, 1993.

[4] M. D. Putro, L. Kurnianggoro and K. -H. Jo, “High Performance and Efficient Real-Time Face Detector on Central Processing Unit Based on Convolutional Neural Network,” IEEE Transactions on Industrial Informatics, vol. 17, no. 7, pp. 4449-4457, 2021.

[5] I. Marin, N. Goga and M. Goga, “Benchmarking MD Systems Simulations on the Graphics Processing Unit and Multi-Core Systems,” 2016 IEEE International Symposium on Systems Engineering (ISSE), pp. 1-5, 2016.

[6] M. Shahbazi, E. Jamshidpour, P. Poure, S. Saadate and M. R. Zolghadri, “Open- and Short-Circuit Switch Fault Diagnosis for Nonisolated DC–DC Converters Using Field Programmable Gate Array,” IEEE Transactions on Industrial Electronics, vol. 60, no. 9, pp. 4136-4146, 2013.

[7] E. Atkin et al. “Development of Data Concentration Method and Its Implementation in a Radiation-Tolerant CMOS Application Specific Integrated Circuit,” Physics of Particles and Nuclei, vol. 52, no. 4, pp. 752–756, 2021.

[8] H. Selvaraj, P. Sapiecha and N. Dhavlikar, “Partitioning of Large HDL ASIC Designs into Multiple FPGA Devices for Prototyping and Verification,” Proceedings Fourth International Conference on Computational Intelligence and Multimedia Applications. ICCIMA 2001, pp. 411-415, 2001.

[9] H. Yan, S. A. Watterson, D. K. Lowenthal, K. Li, R. Krishnan and L. L. Peterson, “Client-Centered, Energy-Efficient Wireless Communication on IEEE 802.11b Networks,” IEEE Transactions on Mobile Computing, vol. 5, no. 11, pp. 1575-1590, 2006.

[10] Y. Fu, S. Yan and T. S. Huang, “Special Issue on Feature-Oriented Image and Video Computing for Extracting Contexts and Semantics,” Computer Vision and Image Understanding, vol. 115, no. 3, pp. 289, 2011.

[11] S. Kirkire et al., “Characterization of High Speed Data Transmission Interface for Future IRS Payloads,” 2013 Nirma University International Conference on Engineering (NUiCONE), pp. 1-6, 2013.

[12] K. -J. Farn et al., “An Authenticate Processing for the Information System in Industrial Technology Research Institute,” Proceedings. 25th Annual 1991 IEEE International Carnahan Conference on Security Technology, pp. 59-67, 1991.

[13] N. Sutisna, L. Lanante, Y. Nagao, M. Kurosaki and H. Ochi, “Live Demonstration: Hardware-Software Co-Verification for Very Large Scale SoC Using Synopsys HAPS Platform,” 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 171-172, 2014.

[14] C. Song et al., “Si Interposer with High Aspect Ratio Copper Filled TSV for System Integration,” 2015 IEEE International Interconnect Technology Conference and 2015 IEEE Materials for Advanced Metallization Conference (IITC/MAM), pp. 245-248, 2015.

[15] J. Kaur, “A Balanced Scorecard for Systemic Quality in Electronic Design Automation: An Implementation Method for an EDA Company,” Sixth International Symposium on Quality Electronic Design (isqed'05), pp. 118-122, 2005.

[16] C. L. Hung, Y. H. Su and A. L. -P. Cheng, “Modeling the Valuation Process of Silicon Intellectual Property in the Semiconductor Industry,” 2007 IEEE International Conference on Industrial Engineering and Engineering Management, pp. 592-596, 2007.

[17] V. Shatravin, D. Shashev and S. Shidlovskiy, “Applying the Reconfigurable Computing Environment Concept to the Deep Neural Network Accelerators Development,” 2021 International Conference on Information Technology (ICIT), pp. 842-845, 2021.

[18] K. Lynn, “Universal Serial Bus (USB) Power Management,” Wescon/98. Conference Proceedings (Cat. No.98CH36265), pp. 194-201, 1998.

[19] C. Yang, H. Yu and Y. Chen, “Deep Sea HD Camera System Based on MIPI Interface,” OCEANS 2014 - TAIPEI, pp. 1-4, 2014.

[20] W. -C. Li, C. -J. Yang and W. -C. Fang, “A Real-time Emotion Recognition System Based on an AI System-On-Chip Design,” 2020 International SoC Design Conference (ISOCC), pp. 29-30, 2020.

[21] N. C. Leng, A. J. C. Har and O. Y. W. Tat, “System Management with Relational Database for Mask Tape-Out,” 2012 4th Asia Symposium on Quality Electronic Design (ASQED), pp. 128-132, 2012.

[22] B. K. Vinay, M. Harihar and A. Killedar, “The FPGA Based Emulation of Complex SoC for ADAS Market on ZeBu-Server,” 2014 International Conference on Advances in Electronics Computers and Communications, pp. 1-4, 2014.

[23] H. -H. Yeb, W. -P. Tu, J. -Z. Shen, T. -H. Yen and S. -H. Huang, “Abstract Bus Interface Unit for ESL Design from TLM 2.0 Communications to the Real Bus Protocol,” 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), pp. 611-614, 2014.

[24] A. Gambi, T. Huynh and G. Fraser, “Automatically Reconstructing Car Crashes from Police Reports for Testing Self-Driving Cars,” 2019 IEEE/ACM 41st International Conference on Software Engineering: Companion Proceedings (ICSE-Companion), pp. 290-291, 2019.

[25] P. Sauge and G. Thuau, “Integrating of Verilog-HDL and VHDL Languages in the SMASH/Sup TM/ Mixed-Signal Multi-Level Simulator,” Proceedings International Verilog HDL Conference and VHDL International Users Forum, pp. 2-6, 1998.

[26] J. Sanguinetti and E. Zhang, "The Relationship of Code Coverage Metrics on High-Level and RTL Code," 2010 IEEE International High Level Design Validation and Test Workshop (HLDVT), pp. 138-141, 2010.