NVDLA軟硬體整合,是一件極需細心釐清的工程,其涵蓋的知識與層面包含硬體架構、硬體作動方式、作業系統資源管理方式、驅動程式架構以及應用程式架構規劃、網路架構以及效能分析等,十分廣泛。需具備眾多的預備知識、工程經驗之外,還需要一點運氣與除錯的靈感與經驗。

精彩內容

1. 硬體使用方式

2. 軟體堆疊架構

3. 範例程式架構 |

硬體使用方式

NVDLA硬體架構,可以參考NVDLA Primer[1],以及深度學習軟硬體加速器探索[2]內有詳細說明。以一軟體工程師拿到一個裝置,必定需要了解此裝置之架構,方能確保不會有錯誤操作的狀況出現。因此熟悉[1]、[2]中提到的相關資料,是進行NVDLA 軟硬體整合的第一步。接下來以軟體工程師角度切入,引導讀者把握以下幾個要點,達到迅速理解NVDLA硬體使用過程需要注意的部份,分別為如下所述:

.資料輸入

由於NVDLA是一專門負責做神經網路加速計算的硬體單元,所以對於輸入資料的排列方式、資料大小以及描述等等需要先有全盤性的了解。幸好NVIDIA在NVDLA開源專案中,提供了對應的驅動程式原始碼以及使用範例。相關資料請到NVDLA Open Source Project, NVDLA SW [3],軟體部份之相關原始碼提供十分具有參考價值之實作。相關內容會在軟體堆疊架構中進行簡介。

.資料輸出

相較於資料輸入,資料輸出的部份更需多關注一個點。資料輸入是程式設計者可以主動控制的過程,例如何時把資料填滿到NVDLA資料輸入緩衝區,程式設計者可以全權處理。但資料輸出部份,牽涉到NVDLA計算工作是否完成,如在NVDLA尚未完成計算的時候,就直接讀取,恐怕會取得錯誤的計算結果,導致後續的處理發生不可預期的錯誤產生。這個部份就跟下個部份的「狀態改變通知」有密切關係。

.狀態改變通知

NVDLA對於計算工作處理過程,提供一些狀態指示用的暫存器。對於常使用微處理器(MCU)、應用處理器(Application Processor)的程式設計者而言,藉由暫存器設定進而操作對應的硬體裝置是十分常見的手法。NVDLA正是藉由一堆暫存器提供外部操作介面與管道。這些暫存器中,可約略分為以下幾個類別: ◆操作、設定相關。 ◆資料輸入相關 ◆資料輸出相關 ◆狀態指示、改變相關 ◆例外、錯誤相關 ◆效能計數相關 在上述類別中,以狀態指示、改變為得知NVDLA計算工作狀態的溝通管道。這些暫存器會跟著NVDLA計算工作狀態,進行對應的更改。而當NVDLA完成某個階段的計算工作後,會適時的發出中斷訊號。因此程式設計者可以在[3]找到對應的中斷處理函式。在[3]的Issues討論區中,常可見關於狀態改變的相關問題討論。其根本原因,大都跟NVDLA的中斷信號沒有發出,導致程式設計者無法取得NVDLA狀態改變通知有關。遇到這種狀況,還有一個方法可以解決,就是使用無窮迴圈主動讀取NVDLA狀態相關的暫存器,但是會造成CPU時間被浪費在無窮迴圈中的問題。

.例外、錯誤處理

例外處理、錯誤處理,是指當硬體出現不該出現的狀況、操作行為等等情況發生,對於整個硬體裝置的狀態,將對應的暫存器之狀態設定為例外或者錯誤發生。這個資訊對於程式設計者而言,是十分重要的訊息來源。在整個NVDLA軟硬體整合過程中,常常發生無窮迴圈的狀況。這個時候,就要花不少時間找尋那個環節出錯。不論是程式碼,或者是NVDLA硬體使用流程,都必須把對應的暫存器的值印出,進行相關狀態解讀與分析,以確定是在那個步驟出錯。特別是對於無法重現例外、錯誤流程的時候,暫存器狀態,是一個很有力的除錯線索之一。

軟體堆疊架構

在NVIDIA提供之開源NVDLA軟體部份中,可以分為以下幾個部份:

.KMD,Kernel Mode Driver[4]。目前提供的參考實作為Linux作業系統。支援的核心版本從4.9.x開始到5.1.x等等。在GitHub專案列表中,可以找到已經移植到不同環境的KMD實作可以參考。整個KMD可以分為二個部份,一個是作業系統相關的部份,主要是針對作業系統驅動程式架構相關、系統資源配置與管理、中斷處理等等部份。如果目標作業系統是Linux的話,還需要了解Linux核心中,關於驅動程式架構部份的相關結構與其對應之操作。特別是針對系統資源配置部份,是移植KMD到Linux系統的關鍵。另外一個是與作業系統無關,可以視為是硬體相關的操作函式庫。熟悉這些程式碼之後,可以很輕鬆的將相關操作,移植到不同的處理器。相關細節不在本文的介紹範圍中,留待後續相關機會再行說明。

.UMD,User Mode Driver [4]。目前提供的參考實作為Linux作業系統。由於是Linux User Mode的程式,因此跟Linux核心版本比較無關,反而跟系統函式庫版本比較有關。在整個UMD架構中,主要分為二個部份。一個為NVDLA Runtime類別,這是整個UMD的核心結構。在程式設計者來說,一個良好的設計、操作介面定義,可以加快整個整合工作。在整合過程中,NVDLA UMD Runtime提供的介面,算是十分清楚且容易明瞭的使用方式。另外一個部份是圍繞著NVDLA UMD Runtime實現的範例程式所需要的相關協助處理函式庫。此部分與NVDLA軟硬體整合較無相關,但是對於範例程式開發有直接關連。對於程式設計者而言,有可以參考的程式原始碼,可以減少不少摸索時間,但是參考的程式原始碼如果是示範錯誤的使用方式,將會帶來不少地雷。對於系統穩定性來說,是很棘手的狀況。

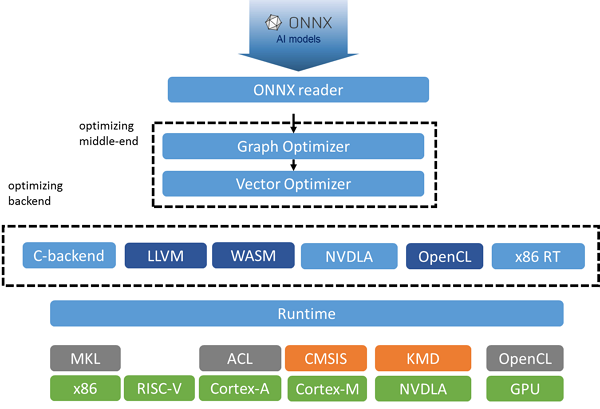

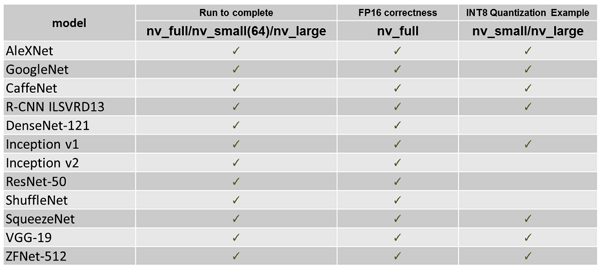

.Compiler [4],編譯神經網路模型給NVDLA執行之編譯器。以NVIDIA NVDLA開源的歷程來說,起初只是提供功能有限的編譯器執行檔,能夠編譯的模型種類不多。之後的改版以及近期更新的編譯器版本,則提供對應的原始碼可以一窺究竟,了解NVDLA編譯器運作方式。以目前開源版本之編譯器測試來說,似乎還有很多需要探究的地方存在,因此NVDLA軟硬體整合,不考慮使用NVIDIA提供之編譯器版本。工研院在NVDLA軟硬體整合過程,引入一個非常重要的合作夥伴,Skymizer [5],提供ONNX為基礎的ONNC編譯器。目前ONNC編譯器支援的硬體架構中,NVDLA支援程度非常高。支援的模型,或者更進一步說明為支援的神經網路運算操作種類極為豐富。相關支援列表請參考圖1、表1。

圖1 Skymizer提供之ONNC編譯器支援架構及系統組成圖

圖1 Skymizer提供之ONNC編譯器支援架構及系統組成圖 表1 ONNC編譯器支援模型對應到NVDLA架構之比較列表

表1 ONNC編譯器支援模型對應到NVDLA架構之比較列表範例程式架構

範例程式以智慧網路攝影機主要訴求之物件偵測功能為主,用NVDLA實現此功能,用以展現相關軟硬體整合,和相關處理工作包含以下幾個部份:

.網路串流接收

.壓縮影像解碼

.影像格式轉換

.NVDLA操作介面

.網路模型後處理

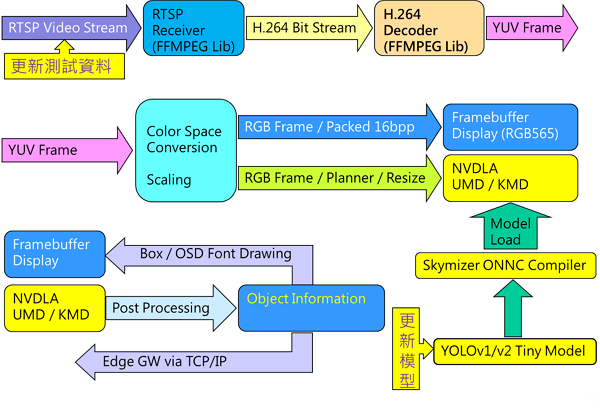

由於範例程式以驗證整個流程為目標,為了減少其他硬體裝置帶來的干擾或者是引入新的資料處理問題,因此採用純軟體處理方式。同時為了降低對其他第三方函式庫的依賴性,除了網路串流接收及影像解碼以FFMPEG[6]實現外,其餘部份皆為自行實作相關的處理函式,期望以最少變更方式實現整個範例程式。接下來針對每個部份進行簡要說明。圖2為整體流程圖;圖3、圖4為實際執行畫面。

圖2 範例程式處理流程圖

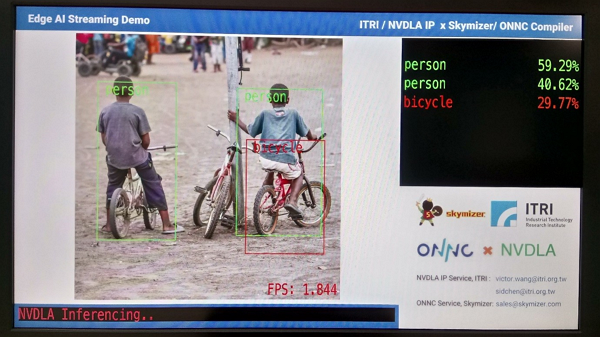

圖2 範例程式處理流程圖 圖3 範例程式執行實際畫面1

圖3 範例程式執行實際畫面1 圖4 範例程式執行實際畫面2

圖4 範例程式執行實際畫面2FFMPEG為一廣泛使用於媒體資料處理之函式庫,用以處理影像、聲音壓縮解壓縮,同時提供許多網路傳輸協定,例如HTTP、RTSP、RTP、RTMP等等,用以處理媒體資料傳輸用;網路串流接收及壓縮影像解碼部份,都是以使用FFMPEG函式庫達成。目前範例程式使用的媒體資料傳輸協定為RTSP,資料傳輸部份走TCP。此一函式庫為常見於知名的開源影音播放軟體、影音資料處理軟體等等。

壓縮影像部份,使用的格式為H.264,支援Baseline以及Main二種Profile。以市面上常見的IP Camera輸出的格式為支援標的,解析度則從320x240一直到720P都可以支援。

影像轉換格式部份,分為二個部份。一為顯示到Linux Frame Buffer上,格式為YUV420P到RGB565,其解析度大小不變。另一個部份為直接寫入至NVDLA輸入緩衝區中,格式為YUV420P到RGB64或者是RGB32。影像解析度則需要跟隨模型輸入大小而有所變化,目前以一個雙線性內插法方式,進行影像大小縮放。

NVDLA操作介面,分為二個層次考量。一是範例程式使用的介面;另一個面向是使用NVDLA UMD Runtime介面。這樣的區分使範例程式可支援不同版本的NVDLA UMD Runtime介面,卻不會造成整個範例程式需要大幅度改寫。意即適當的責任切割,讓變動區域在可控制的範圍內。

網路模型後處理,這個部份牽涉到三個層次的問題:

.資料擺放方式轉換的問題:

由於NVDLA輸出資料緩衝區中,有其對應的資料擺放方式。這點需要參考之前提及的NVDLA UMD範例程式中相關協助處理函式庫的實現方式。

.資料格式轉換的問題:

取得正確的資料輸出後,要處理資料格式轉換的問題,轉換牽涉到模型量化的相關量化係數處理問題,對於量化處理而言,經過量化後要確保精準度的下降程度能夠保持在可接受的範圍內,是一大挑戰。在本文先不做探討,留待之後以專文探討。

.模型後處理計算問題:

網路模型中,輸出階段往往有某些部份需要使用CPU進行計算。對於這個部份,需要做詳細的驗證與確認,方能保證使用同樣的模型,在GPU計算、CPU計算及NVDLA計算後之輸出結果是一致。如有不一致的情況發生就需要進行每個步驟的驗證與確認。

結論

本文中詳述NVDLA軟硬體整合上需要注意的部份以及關鍵點。工研院已成功完成了64運算核心、256運算核心在Xilinx ZCU 102/104 FPGA平台的整合與應用展示,其特色如下所述:

1. 除了NVDLA IP整合、工研院已新增最新DNN模型運算功能,如depth-wise convolution、up-sampling等的支援。工研院以NVDLA之基礎上,新增運算功能,完成相關FPGA驗證,同時可依照客戶需求進行客製化設計服務,在此範例程式中,呈現整合度極高且可朝商品化進行之可行性。

2. Skymizer提供了NVDLA Compiler,並產生確實可被NVDLA IP正確執行的程式碼,相關網路支援陸續擴充中。

3. NVDLA UMD / KMD應用程式範例,實現一個從RTSP串流接收、解碼到使用NVDLA進行物件偵測、圖像識別等等功能。此範例程式為一個完整的智慧攝影機範例,可供DVR相關業者作為參考實現用。

4. 提供INT8模型量化及精度提升的技術服務。原始模型多為FP32型態,而NVDLA支援INT8輕量化的推論運算,工研院可提供符合DLA硬體架構之INT8量化技術。

後續展望可為如下:

1. NVDLA計算效能。深入了解NVDLA效能計數相關暫存器,以及對應的效能解析與改進方式探討是需要的。特別是對於功耗估算,這一步,是需要被仔細驗證。

2. 加速器應用函式庫。以此範例程式設計架構為基礎,用以構建一個應用程式開發容易的加速器應用函式庫設計,是未來應用的基石,值得探討與建構。

更多技術資訊,請洽akiolin@itri.org.tw

參考資料

相關連結: 回180期_AI晶片與系統專輯